# ECE1371 Advanced Analog Circuits Lecture 11

#### SWITCHING REGULATORS

Richard Schreier richard.schreier@analog.com

Trevor Caldwell trevor.caldwell@utoronto.ca

Many thanks to Jonathan Audy for the material from his 2008 ISSCC Tutorial on Power Management and to Prof. Aleks Prodic for his many helpful comments.

#### **Course Goals**

Deepen understanding of CMOS analog circuit design through a top-down study of a modern analog system

The lectures will focus on Delta-Sigma ADCs, but you may do your project on another analog system.

Develop circuit insight through brief peeks at some nifty little circuits

The circuit world is filled with many little gems that every competent designer ought to know.

| Date       | Lecture |    |                           | Ref                | Homework                      |

|------------|---------|----|---------------------------|--------------------|-------------------------------|

| 2008-01-07 | RS      | 1  | Introduction: MOD1 & MOD2 | S&T 2-3, A         | Matlab MOD2                   |

| 2008-01-14 | RS      | 2  | Example Design: Part 1    | S&T 9.1, J&M 10    | Switch-level sim              |

| 2008-01-21 | RS      | 3  | Example Design: Part 2    | J&M 14             | Q-level sim                   |

| 2008-01-28 | тс      | 4  | Pipeline and SAR ADCs     | J&M 11, 13         | Pipeline DNL                  |

| 2008-02-04 |         |    | ISSCC- No Lecture         |                    |                               |

| 2008-02-11 | RS      | 5  | Advanced $\Delta\Sigma$   | S&T 4, 6.6, 9.4, B | $\Delta\Sigma$ Toolbox; Proj. |

| 2008-02-18 |         |    | Reading Week- No Lec      |                    |                               |

| 2008-02-25 | RS      | 6  | Comparator & Flash ADC    | J&M 7              |                               |

| 2008-03-03 | TC      | 7  | SC Circuits               | J&M 10             |                               |

| 2008-03-10 | TC      | 8  | Amplifier Design          |                    |                               |

| 2008-03-17 | TC      | 9  | Amplifier Design          |                    |                               |

| 2008-03-24 | тс      | 10 | Noise in SC Circuits      | S&T C              |                               |

| 2008-03-31 | RS      | 11 | Switching Regulator       |                    |                               |

| 2008-04-07 |         |    | Project Pre               |                    |                               |

| 2008-04-14 | тс      | 12 | Matching & MM-Shaping     |                    | Project Report                |

ECE1371 11-3

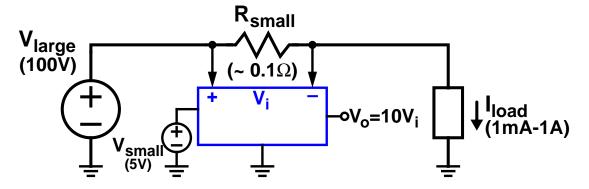

# NLCOTD: High-Side Current Sensing

Want to amplify a small differential voltage which has a large common-mode component

The common-mode component is large because we don't want (or can't have) a resistor in the low-side (ground) path.

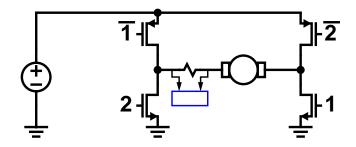

## **NLCOTD: H-Bridge Application**

The sense resistor is switched between the supply and ground, so it is not possible to sense the load current without also sensing a large common-mode component

ECE1371 11-5

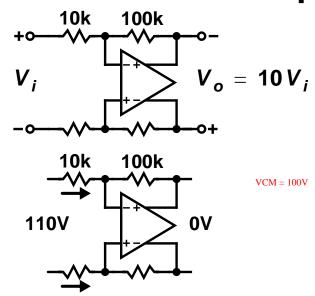

## **NLCOTD:** Differential Amplifier?

- Amplifier sees high CM voltage

- CM current + resistor mismatch ⇒ offset

# Highlights (i.e. What you will learn today)

- 1 Basic Buck and Boost Topologies

- 2 Design Considerations

- 3 Inverting Buck-Boost, SEPIC and Çuk Topologies

- 4 Basic Control Strategies

ECE1371 11-7

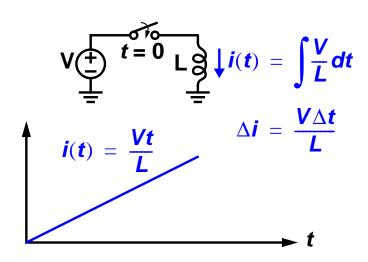

#### **Review: A Switched Inductor**

When a constant voltage is applied across an inductor, the current ramps up with a constant slope

At least until the core starts to saturate.

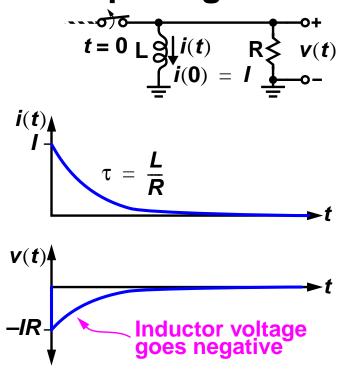

## **Review: Opening the Switch**

ECE1371 11-9

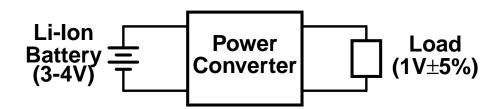

#### The Power Converter Problem

- Battery voltage usually does not equal the desired load voltage

- Often there are many loads and many voltage requirements.

- Even the voltage requirements of a single load can vary with time, e.g. a CPU or DSP with power-saving.

- Battery voltage changes as the battery is charged/discharged

### **Features & Specifications**

- 1 Input/Output Voltages and Currents

- 2 Efficiency

- 3 Voltage ripple

- 4 Line/load regulation; source/sink capability

- 5 Dynamics: response to line/load step; overshoot

- 6 Over-current and over-voltage protection

- 7 Under-voltage lockout; thermal shutdown

- 8 Soft startup; adjustability

- 9 Frequency synchronization

- Plus absolute reliability

if a power converter behaves badly for even 1

μs, the entire system may be destroyed

When in comes to power, mistakes can be forever.

ECE1371 11-11

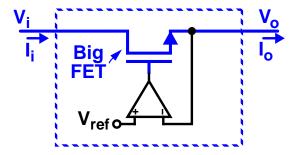

### **Linear Regulator**

- Just a high-power voltage follower

- $-V_{o} < V_{i}$

The "dropout voltage" is the minimum  $V_i - V_o$  required for proper regulator operation.

PMOS FET used to make a low-dropout (LDO) reg.

Inefficient

E.g. if

$$V_i = 4 \text{ V}$$

and  $V_0 = 1 \text{ V}$ , then  $\eta_{\text{max}} = 25\%$ .

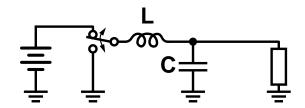

# Switching Regulator— Buck Configuration

- Energy is transferred from the battery to the inductor, capacitor and load when the switch is up

- Energy stored in the inductor is transferred to the capacitor and load when the switch is down

- + Ideally, energy is not dissipated in the regulator Typically,  $\eta >$  90 %.

ECE1371 11-13

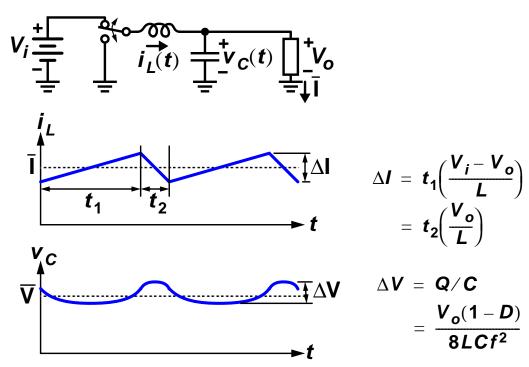

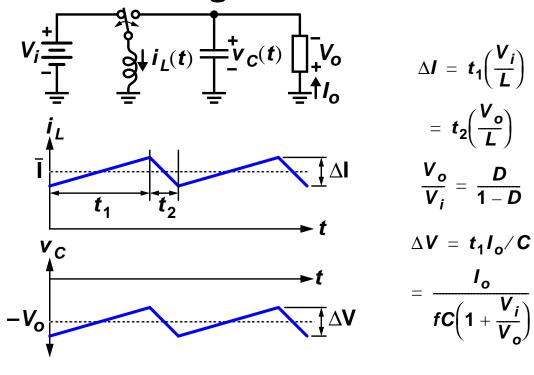

#### **Buck Waveforms-Ideal**

#### **Buck Formulae**

- $V_o = DV_i$ , where  $D \equiv t_1/(t_1 + t_2)$  is the *duty cycle*

- Ripple current is  $\Delta I/2 = (t_2 V_{out})/(2L)$ Up to 40% of peak  $I_o$

• Example:

$$V_i = 4 \text{ V}$$

,  $V_o = 1 \text{ V}$ ,  $T = 1 \mu\text{s}$

$D = V_o / V_i = 0.25 \Rightarrow t_1 = 0.25 \mu\text{s}$ ,  $t_2 = 0.75 \mu\text{s}$

Want  $I_o = 1$  A, and say  $\Delta I = 0.75$  A

$$\Rightarrow L = \frac{t_2 V_{out}}{\Delta I} = \frac{0.75 \,\mu\text{s} \cdot 1 \,V}{0.75 \,A} = 1 \,\mu\text{H}$$

Want  $\Delta V = 20 \text{ mV} \Rightarrow$

$$C = \frac{V_o(1-D)}{8Lf^2\Delta V} = \frac{1 \text{ V} \cdot 0.75}{8 \cdot 1 \text{ } \mu\text{H} \cdot (1 \text{ MHz})^2 \cdot 20 \text{ mV}} = 5 \text{ } \mu\text{F}$$

ECE1371 11-15

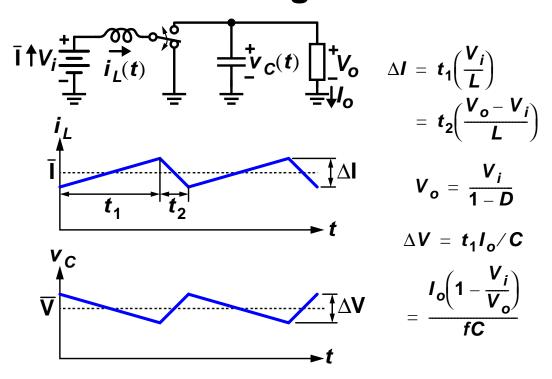

### **Boost Configuration**

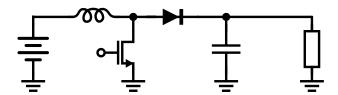

# Boost Converter with Diode (Old-fashioned)

- SPDT switch implemented by a FET and a diode Diode automatically turns on when FET turns off.

Schottky diode minimizes losses.

- Can do the same in a Buck converter, but the efficiency hit is usually unacceptable because V<sub>fwd</sub> is a significant compared to V<sub>out</sub>

- Synchronous rectification is usually preferred

ECE1371 11-17

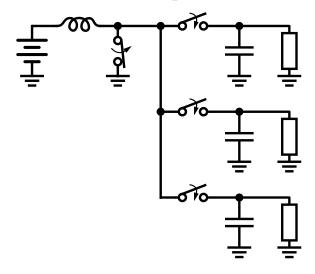

### **Multi-Output Boost**

- Use a single inductor to provide multiple outputs Tricky control problem—a good research topic!

- Can do both buck and boost with more switches

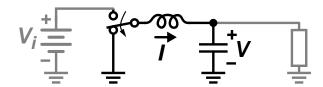

## **Inverting Buck/Boost**

ECE1371 11-19

#### **Loss Mechanisms**

Switch on-resistance

10 m $\Omega$  to 1  $\Omega$ .

Switch capacitance

C<sub>gs</sub>: 100 pF to 1 nF; C<sub>d</sub>: 20 to 200 pF. Limit switching frequency to limit this loss.

Inductor resistance

5 m $\Omega$  to 0.5  $\Omega$ .

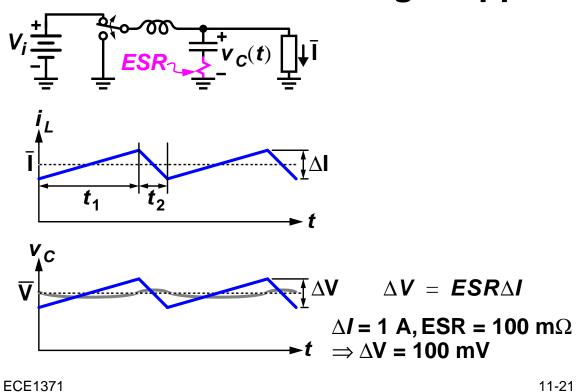

Capacitor resistance

**Equivalent Series Resistance (ESR)**

"Low ESR": 100 m $\Omega$  for C = 10  $\mu$ F

"Ultra-low ESR": 10 m $\Omega$  for C = 10  $\mu$ F

## Effect of ESR on Voltage Ripple

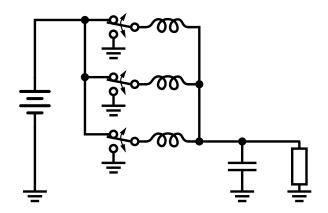

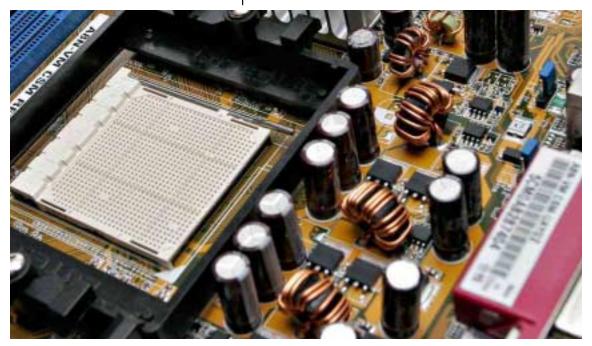

#### **Multi-Phase Buck Converter**

- n synchronized switches drive n inductors in an interleaved manner

- + Reduces ripple voltage Can achieve  $\Delta V \sim 10 \text{mV}$  when driving 100A!

# Example Multi-phase Converter 1.5 V 60 A 3 $\phi$ for AMD Processor

ECE1371 11-23

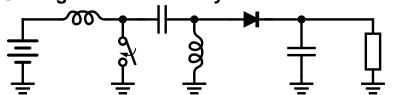

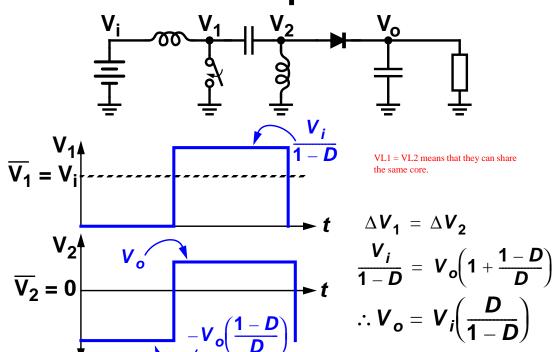

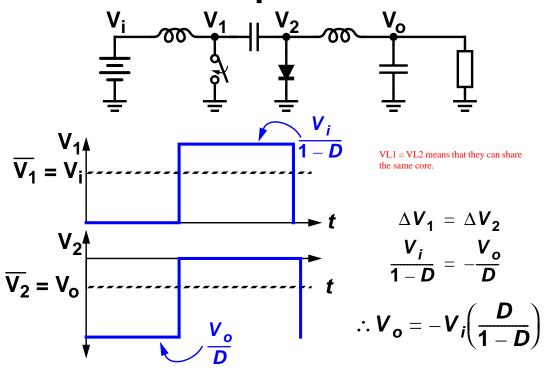

## **Improved Topologies**

**SEPIC:** "Single-Ended Primary Inductor Converter"

+ Input current is continuous

- + Input and output currents are continuous

- Output voltage is negative

## **SEPIC Operation**

ECE1371 11-25

http://www.national.com/an/AN/AN-1484.pdf

## **Cuk Operation**

# Load Removal Buck Converter

If the load current drops to zero, the inductor's energy is dumped into the capacitor and the output voltage goes up

$$\frac{1}{2}LI^{2} + \frac{1}{2}CV^{2} = \frac{1}{2}C(V + \Delta V)^{2}$$

$$\Rightarrow \frac{\Delta V}{V} = \sqrt{\frac{LI^{2}}{CV^{2}} + 1} - 1 \approx \frac{LI^{2}}{2CV^{2}} \sim 10\% \text{ for our ex.}$$

$\Rightarrow$  Need to increase C to make  $\triangle V$  acceptable

ECE1371 11-27

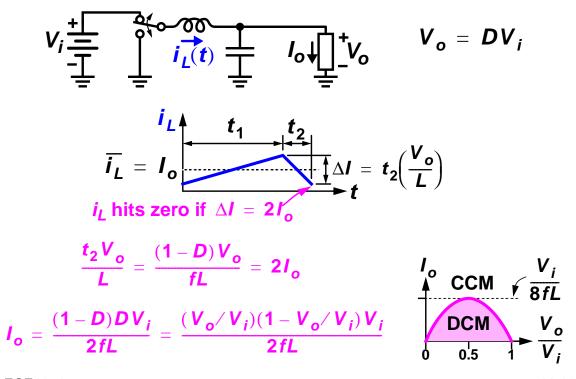

# Exceptional Case— Discontinuous Conduction Mode

- "Switching Regulators are about 20% basic concept, and 80% fixes to problems with the basic concept" [Audy, 2008 ISSCC]

- Discontinuous Conduction Mode (DCM) occurs in a diode-based switcher if the inductor current goes to zero

DCM does not occur if a diode is not used to make the switch, unless a zero-crossing detection circuit is added to the synchronous rectifier

DCM improves η at low I<sub>O</sub>

But since DCM dynamics differ from CCM dynamics, fancier control algorithms are needed.

#### **DCM** in a Buck Converter

ECE1371

11 20

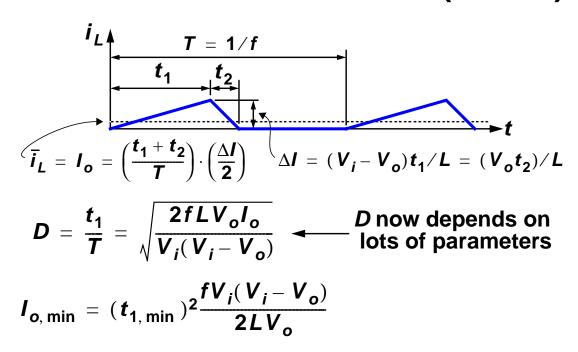

## DCM in a Buck Converter (cont'd)

ECE1371

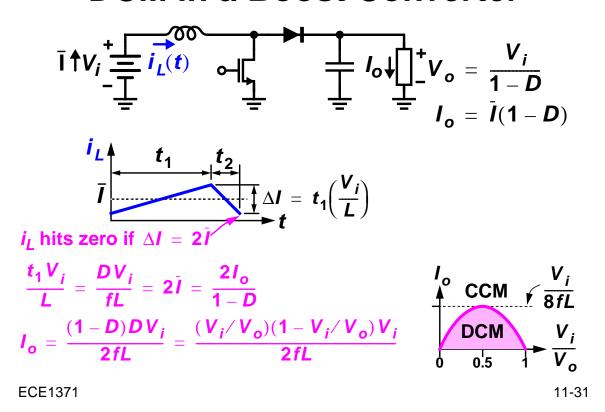

### **DCM** in a Boost Converter

# Control Strategies [Audy 2008]

The control problem involves deciding when to open/close the switch

- Want to achieve a specific V<sub>o</sub>

Except if load current is too great, or if the input voltage is too low, or ...

- SMPS control is a fertile research area

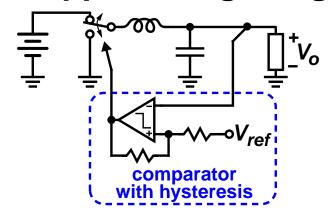

### **Hysteretic Ripple Voltage Regulator**

- If  $V_o < V_{ref}$ , turn on the switch and keep it on until  $V_o > V_{ref} + V_{hyst}$

- + Simple; fast; stable

- Behavior depends on ESR: ill-controlled dynamics & excess ripple; Nothing limits ton

ECE1371 11-33

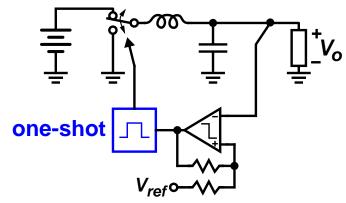

# Constant ton Hysteretic Regulator

- t<sub>on</sub> is fixed

- Need to add circuitry to ensure minimum t<sub>off</sub>

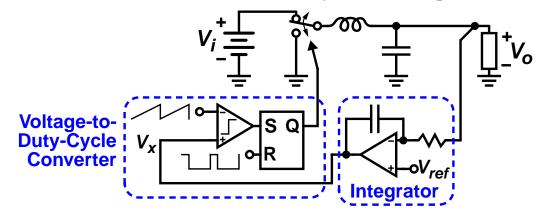

### **Constant-Frequency Voltage-Mode**

- + Frequency is well-controlled (fixed)

- Duty cycle is regulated to achieve desired  $V_o$

- Loop is slow to respond to V<sub>i</sub> changes

Effectively a triple integration: V<sub>i</sub>  $\rightarrow$  i<sub>L</sub>  $\rightarrow$  V<sub>o</sub>  $\rightarrow$  V<sub>x</sub>

ECE1371 11-35

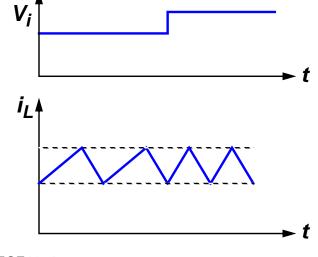

## Other Control Schemes— Ripple Current Control

• In a Buck converter, regulating inductor ripple current  $\Rightarrow$  D tracks  $V_i$  &  $V_o$  changes automatically

- + Fast!

- Still need a slow voltage loop to get desired V<sub>o</sub>

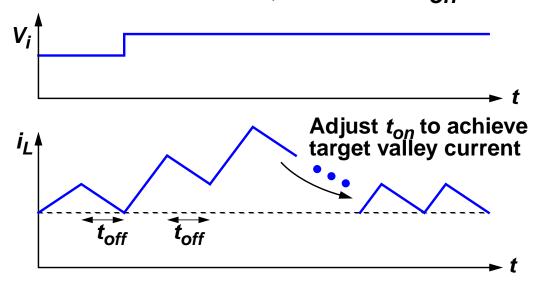

# Valley Current Control Buck converter; Constant $t_{off}$

Average current control is automatic

ECE1371 11-37

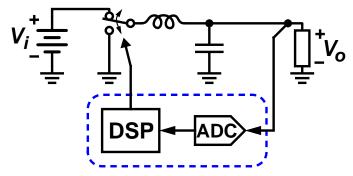

## **Digital Control**

Controlling the switch with digital logic offers many advantages in flexibility, programmability and adaptability, not to mention ease of design!

- ADC only needs a few bits of resolution

- DSP needs a digitally-controlled delay in order to set the on/off times with fine resolution

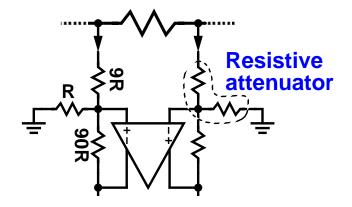

# NLCOTD: High-Voltage Differential Amplifier

- + Amplifier sees low voltages

- Resistor trimming needed for low error AD8206 uses resistors trimmed to 0.01% to get CMRR > 80 dB

ECE1371 11-39

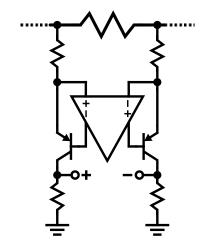

# **NLCOTD: Current-Sense Amplifier**

+ Very low CM current ⇒ less sensitive to mismatch

AD8210 achieves CMRR ~ 100 dB

High-voltage amplifier needed

# **What You Learned Today**

- 1 Basic Buck and Boost Topologies

- 2 Design Considerations

- 3 Inverting Buck-Boost, SEPIC and Çuk Topologies

- 4 Basic Control Strategies