**ECE1371 Advanced Analog Circuits** Lecture 8

#### COMPARATOR & FLASH ADC DESIGN

**Richard Schreier** richard.schreier@analog.com

Trevor Caldwell trevor.caldwell@utoronto.ca

#### **Course Goals**

- Deepen understanding of CMOS analog circuit design through a top-down study of a modern analog system— a delta-sigma ADC

- Develop circuit insight through brief peeks at ٠ some nifty little circuits The circuit world is filled with many little gems that every competent designer ought to know.

ECE1371

8-2

| Date       | Lecture                          |    | Lecture                 | Ref             | Homework          |

|------------|----------------------------------|----|-------------------------|-----------------|-------------------|

| 2012-01-12 | RS                               | 1  | Introduction: MOD1      | ST 2, A         | 1: MOD1 in Matlab |

| 2012-01-19 | RS                               | 2  | MOD2 & MODN             | ST 3, 4, B      | 2: MOD2 in Matlab |

| 2012-01-26 | RS                               | 3  | Example Design: Part 1  | ST 9.1, CCJM 14 | 3: Swlevel MOD2   |

| 2012-02-02 | тс                               | 4  | SC Circuits             | R 12, CCJM 14   | 4: SC Integrator  |

| 2012-02-09 | тс                               | 5  | Amplifier Design        |                 |                   |

| 2012-02-16 | тс                               | 6  | Amplifier Design        |                 | 5: SC Int w/ Amp  |

| 2012-02-23 | Reading Week + ISSCC- No Lecture |    |                         |                 |                   |

| 2012-03-01 | RS                               | 7  | Example Design: Part 2  | CCJM 18         | Start Project     |

| 2012-03-08 | RS                               | 8  | Comparator & Flash ADC  | CCJM 10         |                   |

| 2012-03-15 | тс                               | 9  | Noise in SC Circuits    | ST C            |                   |

| 2012-03-22 | тс                               | 10 | Matching & MM-Shaping   | ST 6.3-6.5, +   |                   |

| 2012-03-29 | RS                               | 11 | Advanced $\Delta\Sigma$ | ST 6.6, 9.4     |                   |

| 2012-04-05 | тс                               | 12 | Pipeline and SAR ADCs   | CCJM 15, 17     |                   |

| 2012-04-12 | No Lecture                       |    |                         |                 |                   |

| 2012-04-19 | Project Presentation             |    |                         |                 |                   |

ECE1371

8-3

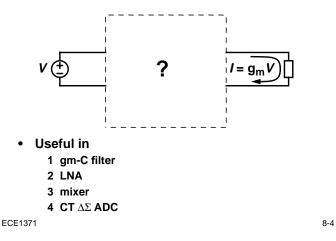

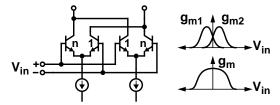

#### **NLCOTD: Linear Transconductor**

#### Highlights (i.e. What you will learn today)

- **1** Operation of Example Comparator Circuit

- 2 Regeneration Time Constant

- 3 Metastability, Probability of Error

- 4 Dynamic Offset

- **5** Other Comparator Circuits

- 6 A Bunch of Transconductor Circuits

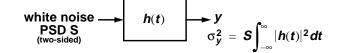

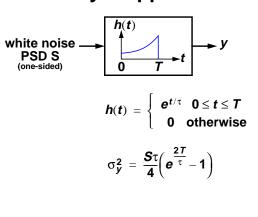

# **Background: Filtered White Noise**

- The power of the output is the product of the PSD and the power gain of the filter

- Example:  $h(t) = \begin{cases} 1 & 0 \le t \le T \end{cases}$

$$\Rightarrow \sigma_y^2 = ST$$

8-5

ECE1371

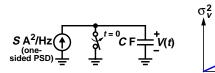

# **Circuits Application: Integrated White Noise** $=\frac{S}{2C^2}t$

"Random Walk" or "Brownian Motion" For any given increment of time  $\Delta t$ , the change in V is a random variable with constant variance  $\delta(t) \equiv V(t) - V(t - \Delta t) \Longrightarrow \sigma_{\delta}^2 = \text{constant}$

ECE1371

# **Today's Application**

**Background: PDF of a Sum**

- Suppose x and y are two independent random variables with probability density functions (PDFs)  $\rho_x(x)$  and  $\rho_v(y)$

- Then the PDF of their sum is the convolution of • the individual PDFs

$$z = x + y \Rightarrow \rho_z(z) = \int_{-\infty}^{\infty} \rho_x(x) \rho_y(z - x) dx$$

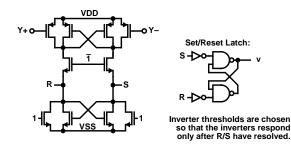

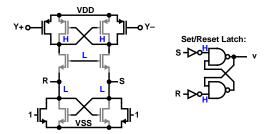

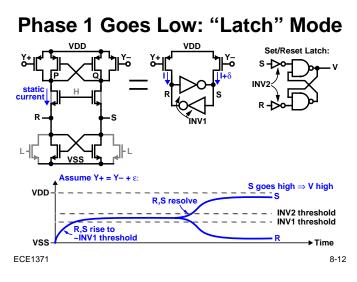

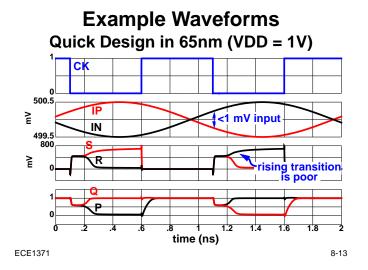

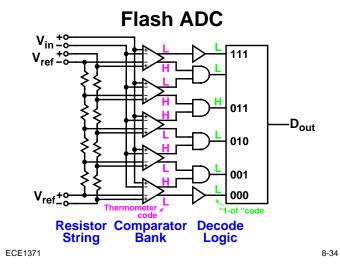

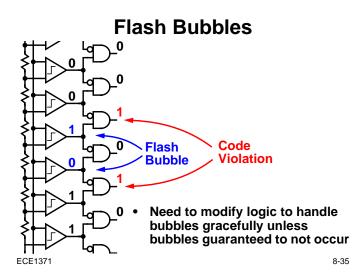

#### **Review: Latched Comparator** From Lecture #7's 1-MHz MOD2

• Falling phase 1 initiates regenerative action S and R connected to a Set/Reset latch.

ECE1371

8-9

ECE1371

8-7

8-10

8-8

# Phase 1 = High: "Reset" Mode

- Grayed-out devices are off ٠  $\Rightarrow$  the active part of the comparator is reset

- R and S are low  $\Rightarrow$  the SR latch is in hold mode ٠

ECE1371

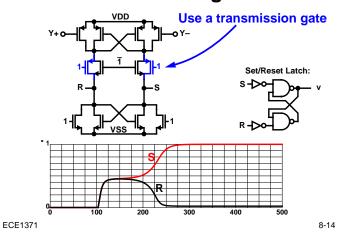

**Better Design**

Responses for Various V<sub>in</sub> Ċκ S V<sub>in</sub> = 10 mV, 1 0.1 mV mV. 0<mark>6</mark> 400 100 300 500 time (ps) ECE1371 8-15

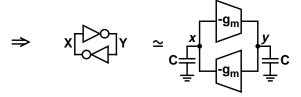

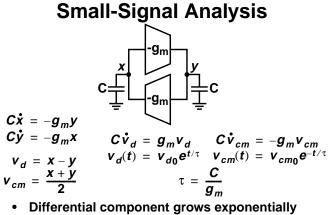

# Latch Mode Dynamics

For V<sub>in</sub> near the trip point, an inverter is essentially just a transconductor:

So near balance the comparator looks like this: ٠

CM component decays exponentially •

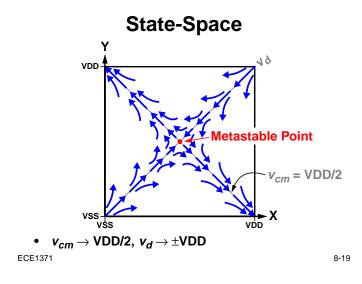

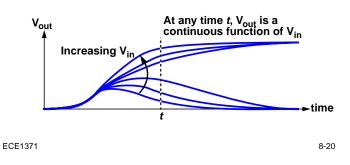

### **Metastability**

- Metastability is fundamentally unavoidable

- Assuming the universe is continuous and deterministic, a comparator can be unresolved for any length of time

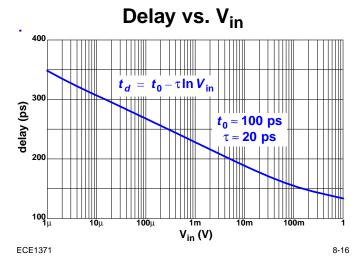

# Probability of Error, PE

$P_E = P\{$ not resolved by time  $t\}$

$$= \boldsymbol{P} \left\{ \boldsymbol{V}_{in} < \exp\left(\frac{\boldsymbol{t} - \boldsymbol{t}_0}{\tau}\right) \right\}$$

- Take  $t_0 = 100 \text{ ps and } \tau = 20 \text{ ps}$

- Then for t = 500 ps (1 GHz clock with a halfcycle between the comparator's clock and the clock of the subsequent latch),

$$P_{E} = P\{|V_{in}| < 2 \text{ nV}\}$$

Assuming V<sub>in</sub> is uniformly distributed in [-0.5, +0.5] V, P<sub>E</sub> = 2×10<sup>-9</sup> Metastability occurs twice a second!

ECE1371

# **Quantized Charge Helps?**

- If C = 20 fF, then 1 electron yields 8 μV

- V<sub>in</sub> = 2 nV and hence metastability impossible?

- Unless V<sub>offset</sub> is within 2 nV of one of the discrete V<sub>in</sub> levels, metastability can't happen

- But if V<sub>offset</sub> is within 2 nV of an allowed V<sub>in</sub> level, metastability will be abnormally frequent

- Offset drift will tend to make metastability appear/disappear sporadically (?)

ECE1371

8-21

# **Noise Helps?**

- kT/C = 500  $\mu$ V, so it is impossible to guarantee that metastability will result even if V<sub>in</sub> = 0

- + Noise does help a comparator resolve if it is metastable

- But for any given noise (random initial condition), there is always an input which results in metastability

- Noise makes it hard to set initial conditions that will result in metastability, but does not reduce the probability of error

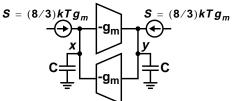

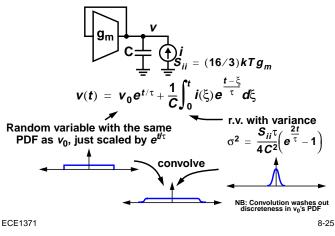

# What About Noise During Regeneration?

Noise from the g<sub>m</sub>s prevents metastability?

ECE1371

#### **Differential Circuit**

# Let's "Make Numbers"

- Assume  $g_m = 1 \text{ mA/V}$ , C = 20 fF, t = 400 ps  $\Rightarrow \tau = 20 \text{ ps}$ ; 20 $\tau$  to resolve

- If v<sub>0</sub> uniformly distributed in [-2,+2] mV, then 1<sup>st</sup> term is uniformly distributed in [-1,+1] MV

- Standard deviation of 2<sup>nd</sup> term is 250 kV Equivalent to a 0.5-mV initial condition

- Noise during regeneration helps when the input is known to be small, but is usually negligible compared to the exponential growth of the initial conditions

ECE1371

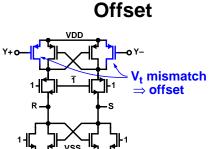

Obvious sources of offset include mismatch in the input differential pair as well as mismatch in the regenerating devices

ECE1371

#### **Dynamic Offset** $\downarrow^{VDD}$ $\downarrow^{VDD}$ $\downarrow^{V+=Y-}$ $\downarrow^{VDD}$ $\downarrow^{V+=Y-}$ $\downarrow^{VDD}$ $\downarrow^{VDD}$ $\downarrow^{VDD}$ $\downarrow^{VDD}$ $\downarrow^{V+=Y-}$ $\downarrow^{VDD}$ $\downarrow^{VDD}$ $\downarrow^{VDD}$ $\downarrow^{V}$ $\downarrow^{V}$ $\downarrow^{VDD}$ $\downarrow^{V}$ $\downarrow^{V$

- Mismatched parasitic capacitance also causes offset 20 mV/fF for this comparator!

- Bad design- Can fix this!

ECE1371

8-27

8-28

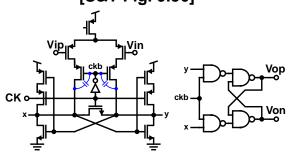

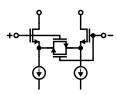

#### Improved Comparator [S&T Fig. 9.36]

- Reset when CK = 1; regenerates when CK = 0

- x & y don't step if biased properly Mismatch in overlap capacitance still a problem.

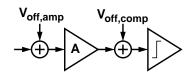

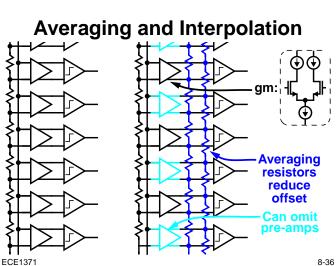

# **Reducing Offset with a Preamp**

$V_{off,tot} = V_{off,amp} + V_{off,comp} / A$

- + Comparator offset is reduced by preamp gain Amplifier offset dominates.

- + Amplifier also isolates driving stage from "charge kickback"

- Amplifier bandwidth limits speed, especially recovery from overload

ECE1371

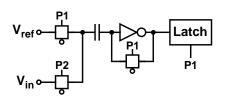

#### **Auto-zeroed SC Comparator** [J&M Fig 13.17]

- During P1, the inverter/amplifier is biased at its • threshold/offset voltage

- During P2, the difference between V<sub>in</sub> and V<sub>ref</sub> is • amplified

ECE1371

8-31

8-33

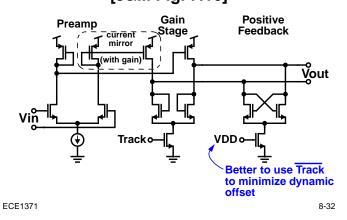

#### **Comparator with Preamp** [J&M Fig. 7.16]

**Two-Stage Comparator** [J&M Fig 7.17] current Reset Ц Vout Vin Ŧ Reset C Positive Logic-level Preamp Feedback Restoration

Precharges regeneration nodes low & • digital output nodes high

ECE1371

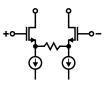

#### NLCOTD: Linear Transconductors Degenerated Differential Pair

+ Simple!

ECE1371

-  $V_{qs}$  varies nonlinearly with  $I_{out} \Rightarrow g_m$  is nonlinear

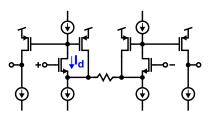

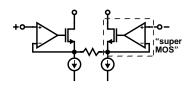

# Force Constant V<sub>gs</sub>

- $I_d$  constant  $\Rightarrow$   $V_{qs}$  constant

- Linearity dependent on current-mirror linearity

8-37

8-39

ECE1371

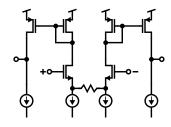

- V<sub>gs</sub> of input devices replicated in cascodes and distortion-cancelling current injected into output

- + All NMOS  $\Rightarrow$  fast

- Cancellation depends on matching Should tie bulk to source?

ECE1371

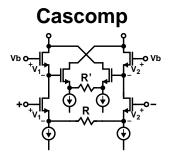

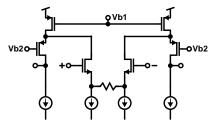

#### Add Op Amps

- + Linearity limited only by op amp gain and BW

- + High output resistance

- Output compliance depends on input swing

ECE1371

8-40

8-38

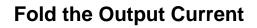

# **Mirror the Output Current**

- + Output compliance is VDD 2 V<sub>dsat</sub>

- Top of differential pair at VDD  $V_{qs}$

- + Increased headroom for differential pair

- + Increased output resistance

#### Multi-Tanh Doublet [Gilbert JSSC Dec. 1998]

- With BJTs, ratioing the emitter areas creates a well-controlled offset

- With the right offset, the cubic term in the nonlinearity is zero!

ECE1371

#### ECE1371

8-43

#### **MOS Quad**

Supposedly can get less distortion than a degenerated differential pair by fiddling with W/L

8-44

What You Learned Today

- 1 Operation of Example Comparator Circuit

- 2 Regeneration Time Constant

- 3 Metastability, Probability of Error

- 4 Dynamic Offset

- **5** Other Comparator Circuits

- 6 A Bunch of Transconductor Circuits

ECE1371