#### ECE1371 Advanced Analog Circuits Lecture 4

# **EXAMPLE DESIGN-PART 2**

Richard Schreier richard.schreier@analog.com

Trevor Caldwell trevor.caldwell@utoronto.ca

## **Course Goals**

- Deepen understanding of CMOS analog circuit design through a top-down study of a modern analog system— a delta-sigma ADC

- Develop circuit insight through brief peeks at some nifty little circuits

The circuit world is filled with many little gems that every competent designer ought to know.

| Date       | Lecture (M 13:00-15:00)  |    | ecture (M 13:00-15:00)                           | Ref                              | Homework                                 |

|------------|--------------------------|----|--------------------------------------------------|----------------------------------|------------------------------------------|

| 2015-01-05 | RS                       | 1  | MOD1 & MOD2                                      | ST 2, 3, A                       | 1: Matlab MOD1&2                         |

| 2015-01-12 | RS                       | 2  | $\mathbf{MODN} + \Delta \Sigma \mathbf{Toolbox}$ | ST 4, B                          | <b>2:</b> $\Delta \Sigma$ <b>Toolbox</b> |

| 2015-01-19 | RS                       | 3  | Example Design: Part 1                           | ST 9.1, CCJM 14                  | 3: Swlevel MOD2                          |

| 2015-01-26 | RS                       | 4  | Example Design: Part 2                           | CCJM 18                          |                                          |

| 2015-02-02 | ТС                       | 5  | SC Circuits                                      | R 12, CCJM 14                    | 4: SC Integrator                         |

| 2015-02-09 | ТС                       | 6  | Amplifier Design                                 |                                  |                                          |

| 2015-02-16 | Reading Week– No Lecture |    |                                                  |                                  |                                          |

| 2015-02-23 | ТС                       | 7  | Amplifier Design                                 |                                  | 5: SC Int w/ Amp                         |

| 2015-03-02 | RS                       | 8  | <b>Comparator &amp; Flash ADC</b>                | CCJM 10                          |                                          |

| 2015-03-09 | ТС                       | 9  | Noise in SC Circuits                             | ST C                             |                                          |

| 2015-03-16 | RS                       | 10 | Advanced $\Delta\Sigma$                          | ST 6.6, 9.4                      | Project                                  |

| 2015-03-23 | ТС                       | 11 | Matching & MM-Shaping                            | ST 6.3-6.5, +                    |                                          |

| 2015-03-30 | тс                       | 12 | Pipeline and SAR ADCs                            | CCJM 15, 17                      |                                          |

| 2015-04-06 | Exam                     |    |                                                  | Proj. Report Due Friday April 10 |                                          |

| 2015-04-13 | Project Presentation     |    |                                                  |                                  |                                          |

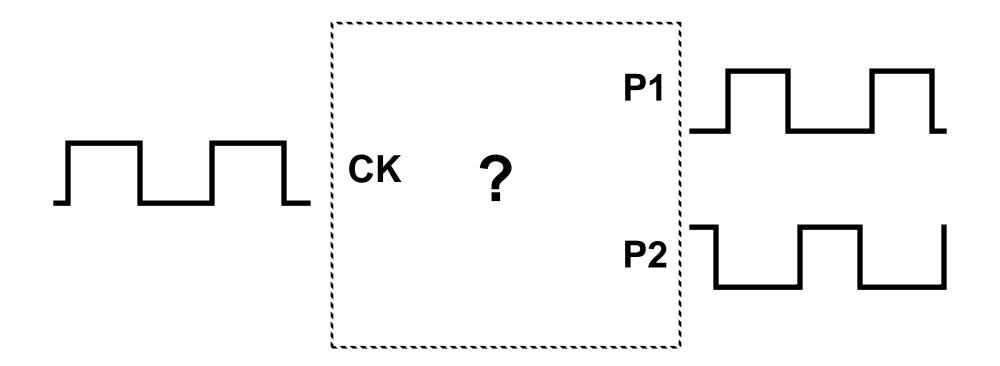

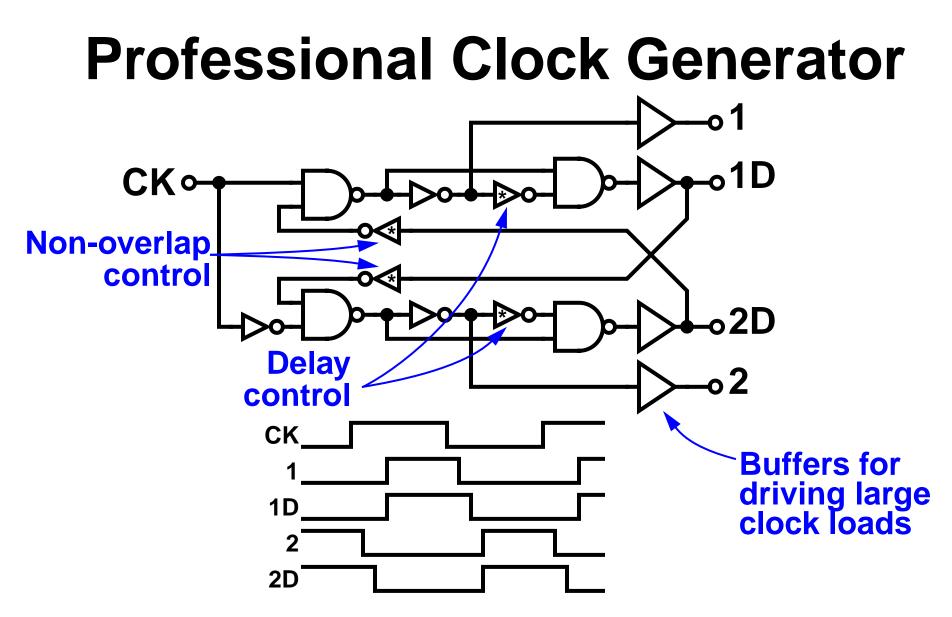

# NLCOTD: Non-Overlapping Clock Generator

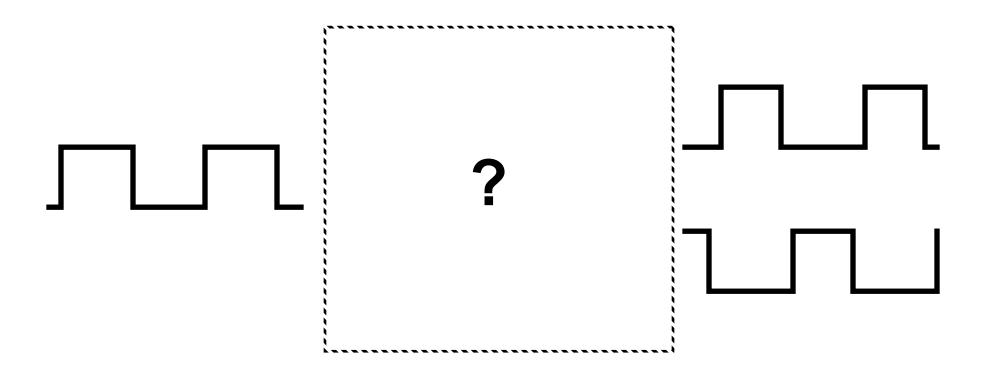

• Our SC circuits require two non-overlapping clocks. How do we generate them?

#### Highlights (i.e. What you will learn today)

- 1 Transistor-level implementation of MOD2 op-amp, SC CMFB, comparator, clock generator

- 2 MOD2 variants

- 3 Variable quantizer gain

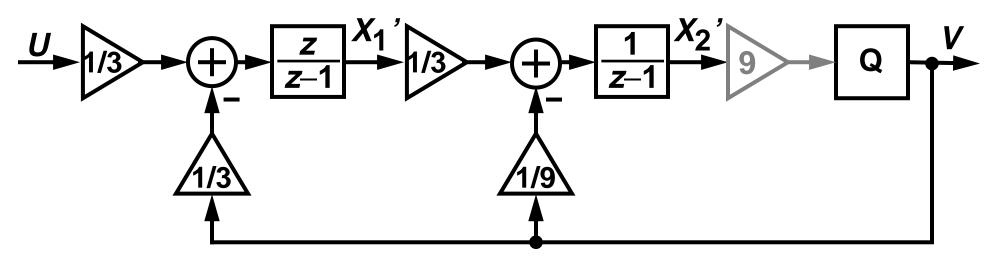

#### **Scaled Block Diagram**

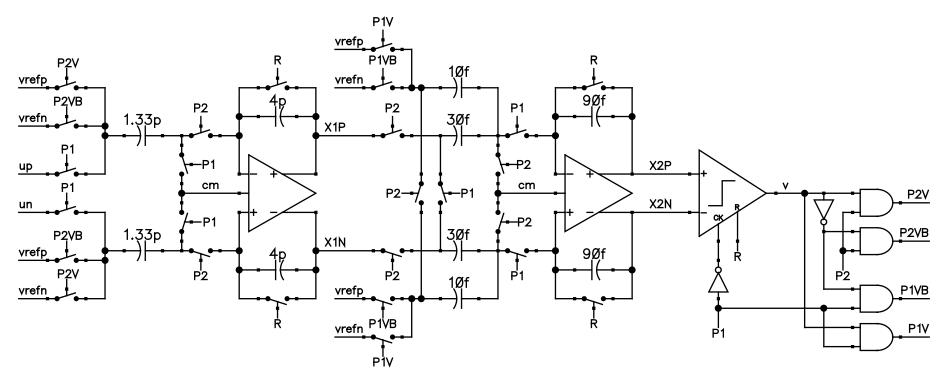

## **Review: Schematic**

- 1<sup>st</sup>-stage capacitor sizes set for SNR = 100 dB

@ OSR = 500 and -3-dBFS input

V<sub>ref</sub> = 1V and the full-scale input range is ±1 V.

- 2<sup>nd</sup>-stage capacitor sizes set by minimum allowable capacitance

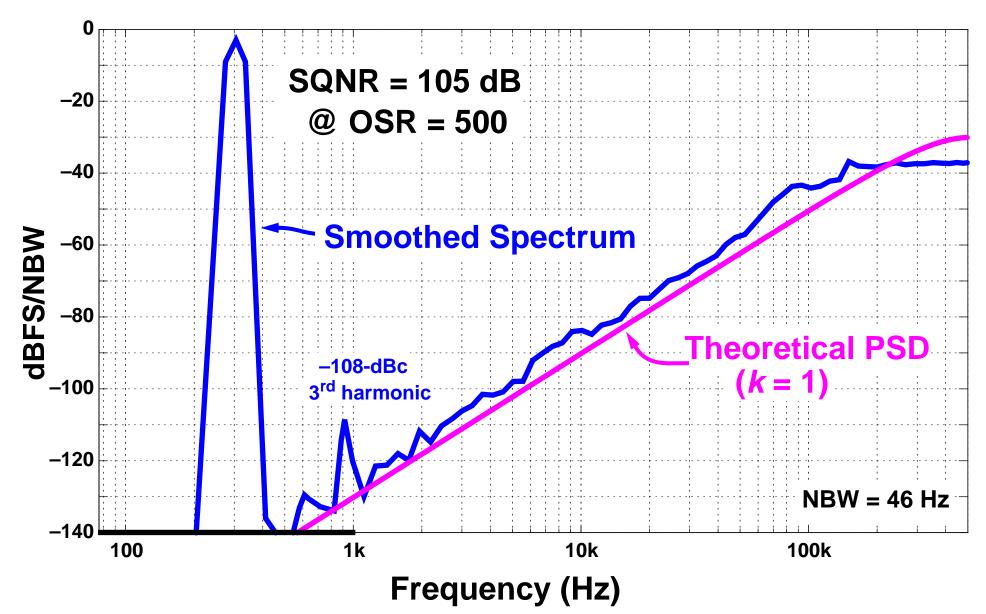

## **Review: Simulated Spectrum**

# **Review: Implementation Summary**

- 1 Choose a viable SC topology and manually verify timing

- 2 Do dynamic-range scaling

You now have a set of capacitor ratios.

Verify operation.

- ✓ 3 Determine absolute capacitor sizes Verify noise.

- >> 4 Determine op-amp specs and construct a transistor-level schematic Verify.

- 5 Layout, fab, debug, document, get customers, sell by the millions, go public, ...

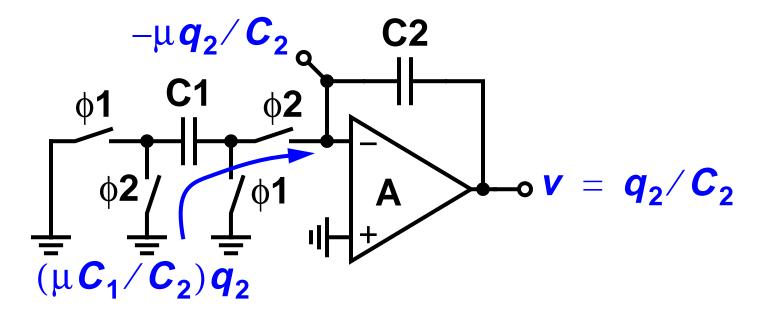

#### Effect of Finite Op Amp Gain Linear Theory

- Suppose that the amplifier has finite DC gain A. Define  $\mu = 1/A$ .

- To determine the effect on the integrator pole, let's look at our SC integrator with zero input:

• A fraction of  $q_2$  leaks away each clock cycle:

$$q_2(n+1) = (1-\varepsilon)q_2(n),$$

where  $\varepsilon = \mu C_1 / C_2$

- Thus, the integrator is lossy, with a pole at  $z = 1 \varepsilon$

- Q: How big can ε get before the effect becomes significant?

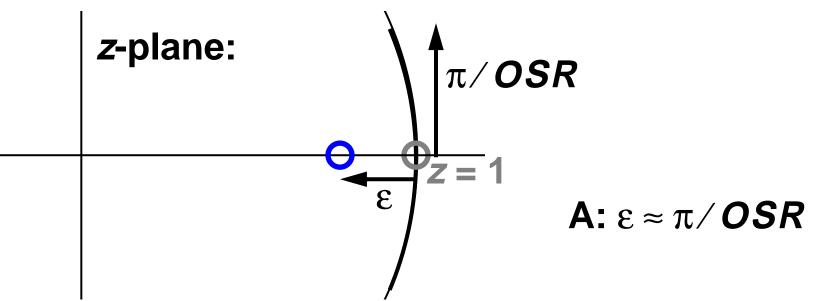

#### Op Amp Gain Requirement Linear Theory

According to the linear theory, finite op amp gain should not degrade the noise significantly as long as

$A > (C_1 / C_2)(OSR / \pi)$

- For our implementation of MOD2, in which  $C_1/C_2 = 1/4$  and OSR = 500, this leads to A > 40 = 32 dB, which is quite a lax requirement!

- As OSR is decreased, the gain requirement goes down

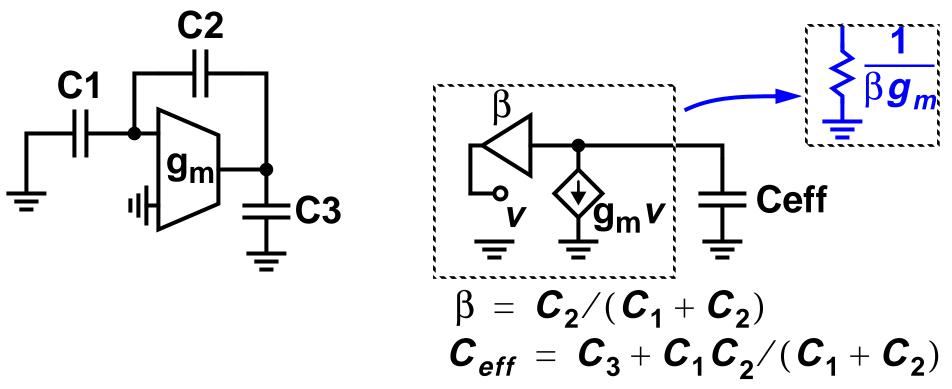

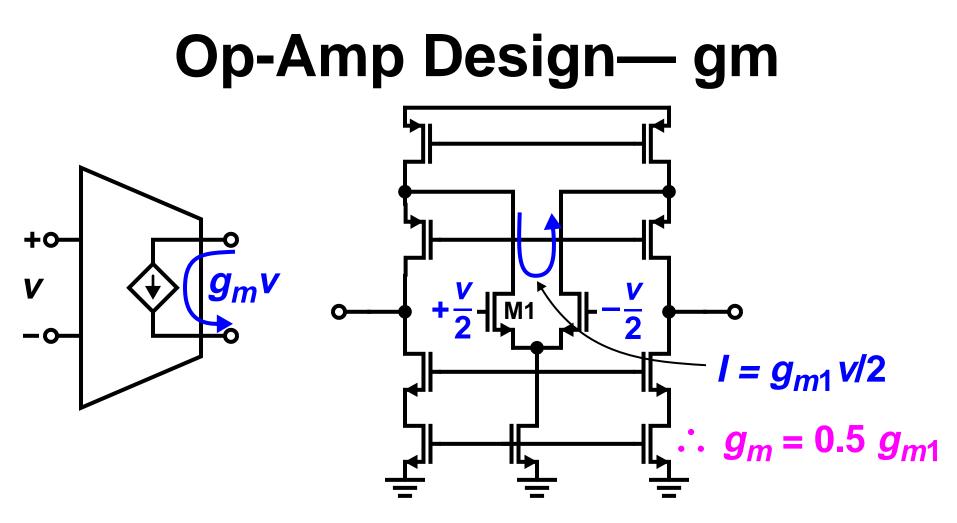

#### Op Amp Transconductance Settling time

• Model the op amp as a simple  $g_m$ :

• This is a single-time-constant-circuit with  $\tau = C_{eff} / (\beta g_m)$

ECE1371

# **Settling Requirements**

- If g<sub>m</sub> is linear, incomplete settling has the same effect as a coefficient error and thus g<sub>m</sub> can be very low

- In practice, the g<sub>m</sub> is not linear and we need to ensure nearly complete settling

- As a worst case scenario, let's require transients to settle to 1 part in 10<sup>5</sup>

This should be more than enough for –100 dBc distortion.

# Settling Requirements (cont'd)

- If linear settling is allocated 1/4 of a clock period, we want  $\exp\left(-\frac{T/4}{\tau}\right) = 10^{-5}$ , or  $\tau = \frac{T}{4\ln 10^5} = 20$  ns and thus  $g_m = \frac{C_{eff}}{\beta \tau} = \frac{C_{eff}}{\beta} 4 f_s \ln 10^5$

- For INT1 of our MOD2:

$$C_{eff} = 0.5 \left( \frac{4p \cdot 1.33p}{4p + 1.33p} + 30f \right) = 0.5 \text{ pF}^*$$

$\beta = 3/4$

$f_s = 1 \text{ MHz}$

$g_m = 30 \mu \text{A/V}$

\*. 0.5 comes from the single-ended to differential translation. ECE1371 4-15

# Slewing

• The maximum charge transferred through C1 is

$$u_{p,max} = \underbrace{0.5 \text{ V}}_{0} C1$$

$$\int_{0}^{\infty} \sqrt{2} \left( \int_{0}^{\infty} q_{max} \right) = C_{1} \cdot 1\text{ V} = 1.33 \text{ pC}$$

$$v_{refn} = -0.5 \text{ V}$$

• If we require the slew current to be enough to transfer  $q_{max}$  in 1/4 of a clock period, then

$$I_{slew} = \frac{q_{max}}{T/4} \approx 5 \ \mu A$$

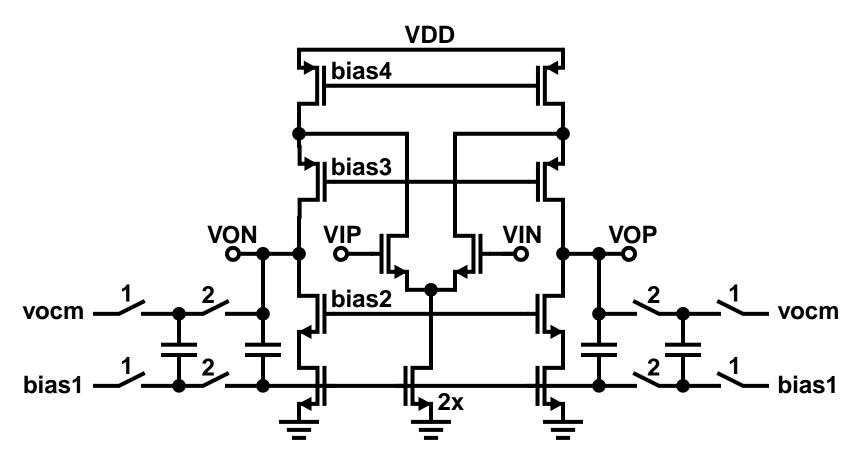

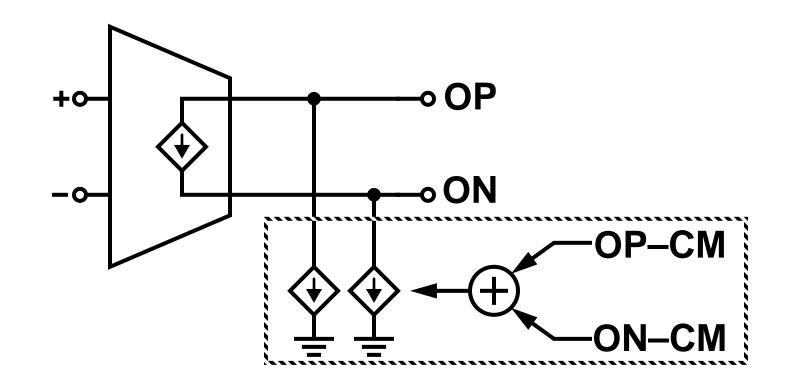

# **Building Block– Op Amp**

Folded-cascode op-amp with switched-capacitor common-mode feedback

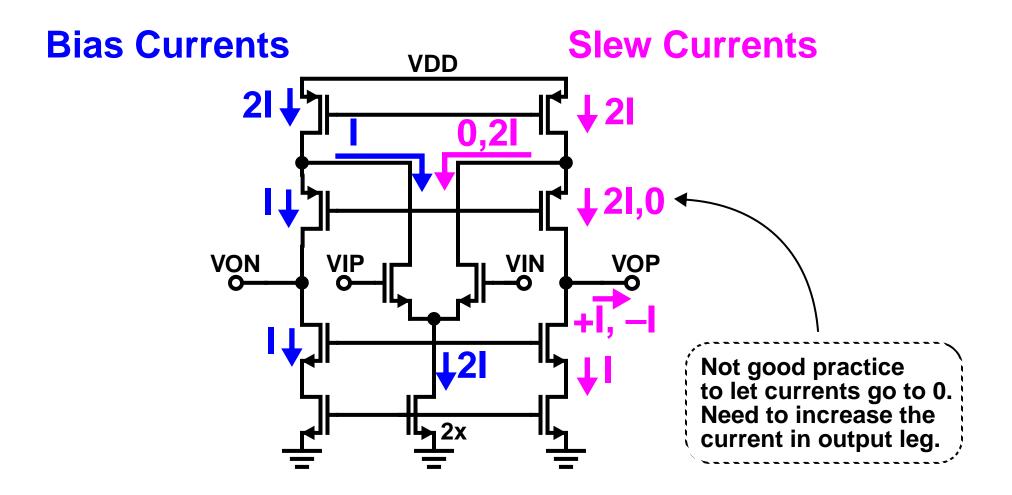

# **Op-Amp Design— Bias Current**

• Slew constraint dictates I >5 μA

- Square-law MOSFET model:  $g_{m1} = (2I_D)/(\Delta V)$

- $I_D = 5 \ \mu A, \ g_m \ge 30 \ \mu A/V \Rightarrow \Delta V \le 0.33 \ V$ Usually  $\Delta V \approx 200 \ mV$ , so we should be able to get high enough  $g_m$ .

ECE1371

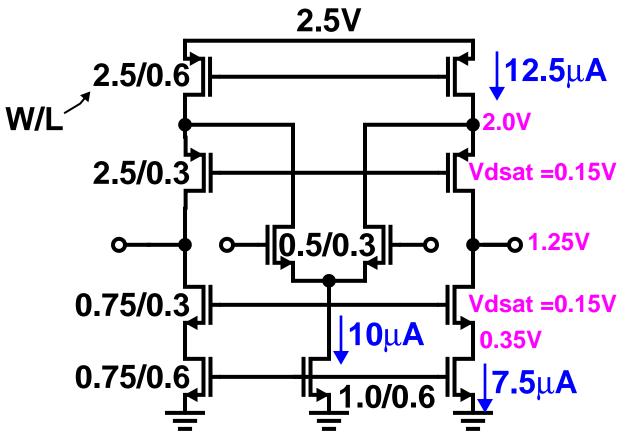

## **Transistor Sizes & Bias Point**

- Allowable swing is +0.6 V, -0.75 V

- Simulated  $g_m = 36 \mu A/V$ , A = 48 dB $g_m$  is high enough and the gain is  $6 \times$  required.

## Ideal Common-Mode Feedback

• Can use this circuit to speed up the simulation

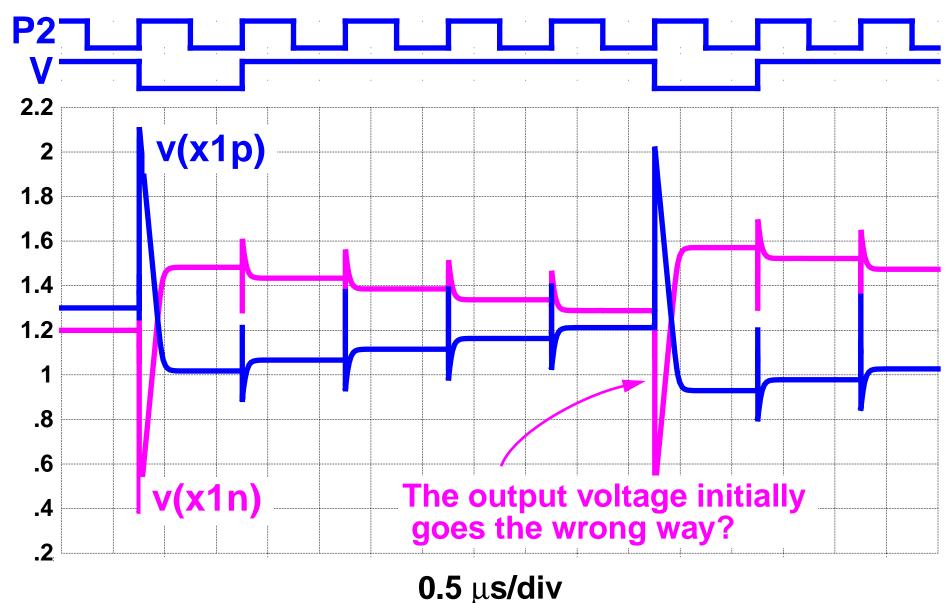

#### **Simulated Waveforms**

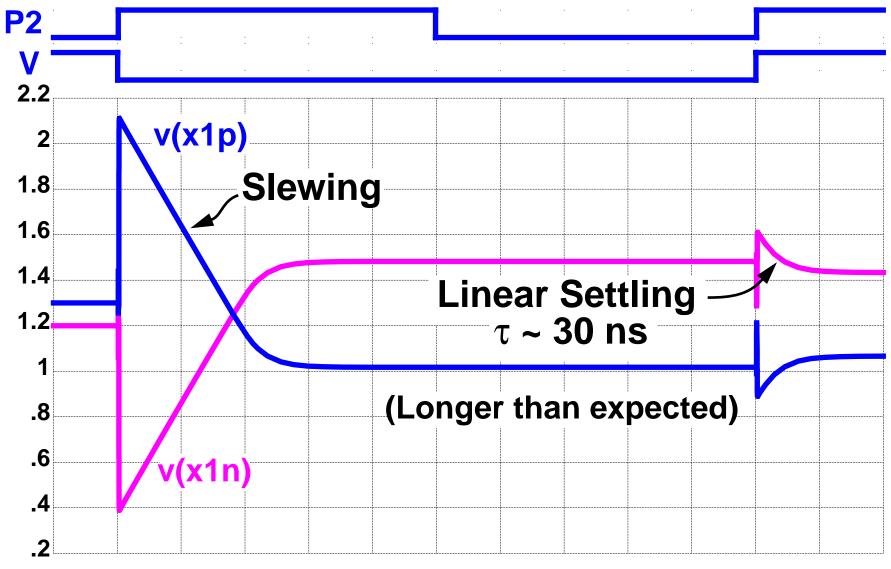

#### **Expanded Waveforms**

100 ns/div

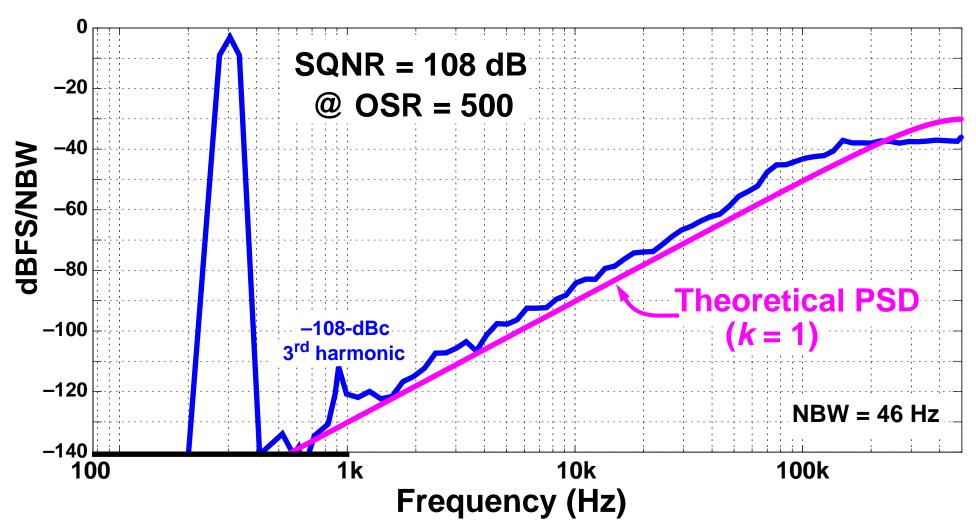

# **Simulated Spectrum**

This was too easy! Although this one simulation *did* take an hour.

ECE1371

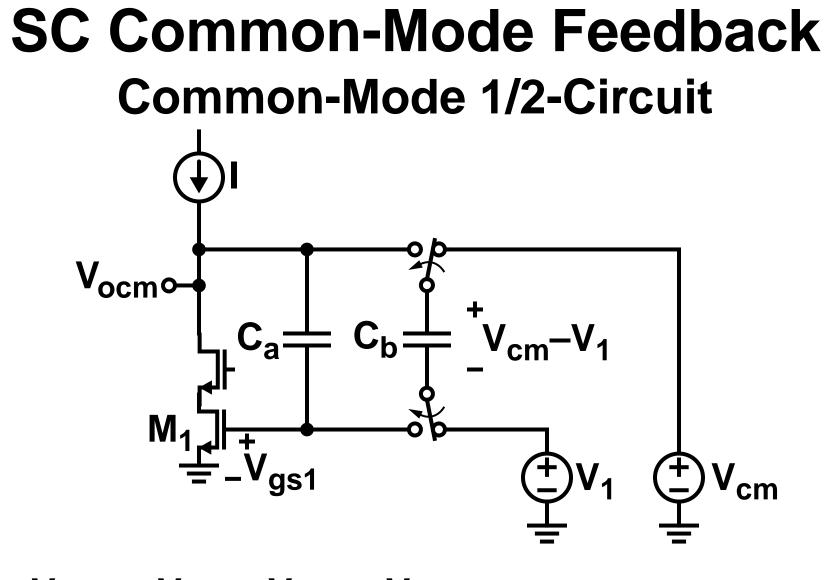

•

$$V_{ocm} = V_{cm} + V_{gs1} - V_1$$

If  $V_1 = V_{gs1}$ , then  $V_{ocm} = V_{cm}$ .

ECE1371

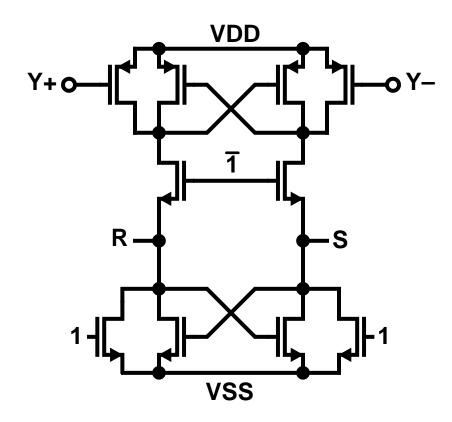

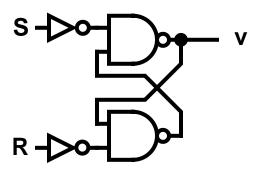

## **Latched Comparator**

Set/Reset Latch:

Inverter thresholds are chosen so that the inverters respond only after R/S have resolved.

• Falling phase 1 initiates regenerative action S and R connected to a Set/Reset latch.

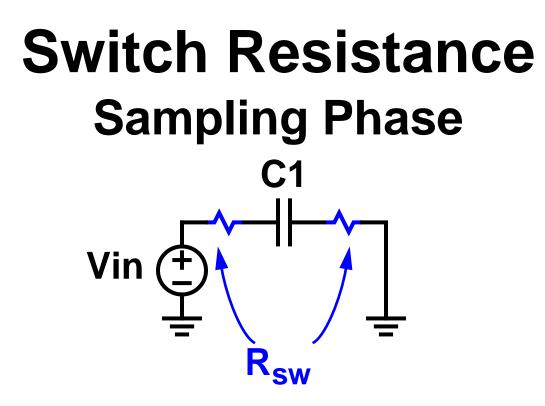

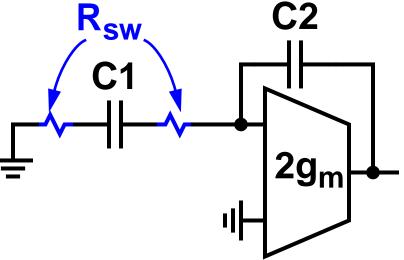

- If R<sub>sw</sub> is constant, its has only a filtering (linear) effect, which is benign

- Unfortunately, the on-resistance of MOS switches varies with V<sub>gs</sub> (and hence V<sub>in</sub>)

- $\Rightarrow$  Must make MOS switches large enough

# Switch Resistance Integration Phase

Differential Half-Circuit:

- $R_{sw}$  increases the settling time by a factor of  $1 + 4g_m R_{sw}$

- $\Rightarrow \quad \text{Set } \boldsymbol{R}_{sw} \leq \frac{1}{40 g_m} \text{ to make the increase in } \tau \text{ small}$

- So in our MOD2, we want  $R_{sw} \le 0.75 \text{ k}\Omega$ . BTW, my simulation used  $R_{sw} = 1 \text{ k}\Omega$  and was OK.

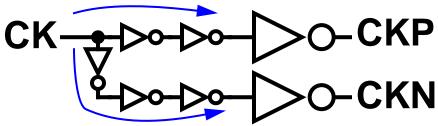

## NLCOTD: Non-Overlapping Clock Generator

# **Non-Overlapping Clock Generator** CKO 0 P1 **P2** CK **P1 P2**

• Non-overlap time set by NOR's *t*<sub>PLH</sub>

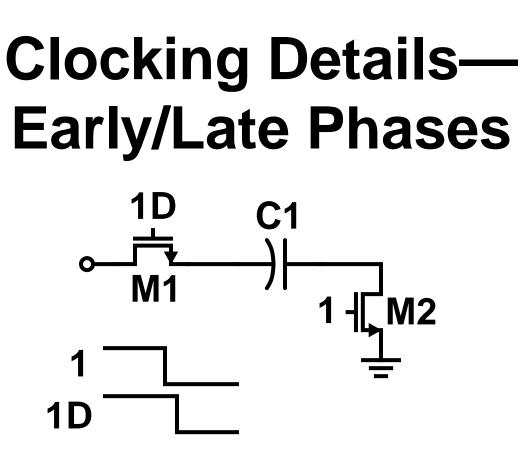

- Charge injected via M1 is (non-linearly) signaldependent, whereas charge injection from M2 is signal-independent

- ⇒ Open M2 (early) then open M1 (late) so that charge injected from  $C_{gs1}$  cannot enter C1

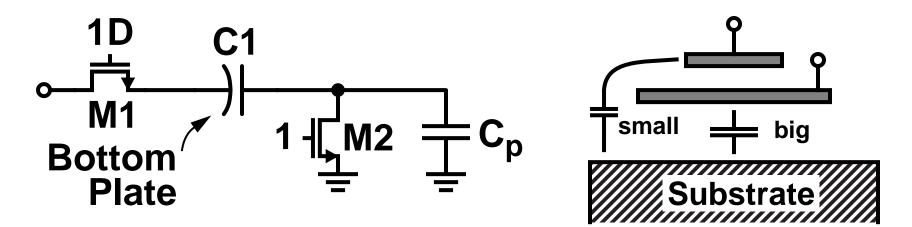

# Clocking Details— Bottom-plate sampling

- Parasitic capacitance on the right terminal of C1 degrades the effectiveness of early/late clocking

- C<sub>p</sub> for the top plate is smaller, so use the top plate for the right terminal and the bottom plate for the left

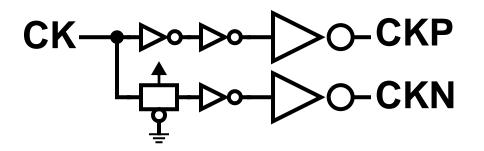

# **Complementary Clock Alignment**

- We need complementary clocks if transmission gates are used for the switches

- **Q: How do we align them?**

- A: Carefully size the inverters relative to their capacitive loads, or use a transmission gate to mimic an inverter delay:

Need to match delay of 3 INVs to 2 INVs

• To maximize the time available for settling, make the early and late phases start at the same time

# **Review: Implementation Summary**

- 1 Choose a viable SC topology and manually verify timing

- $\checkmark$  2 Do dynamic-range scaling

- ✓ 3 Determine absolute capacitor sizes

- 4 Determine op-amp specs and construct a transistor-level schematic Verify. Verify. Verify.

- 5 Layout, fab, debug, document, get customers, sell by the millions, go public, ...

This last step is an "exercise for the reader."

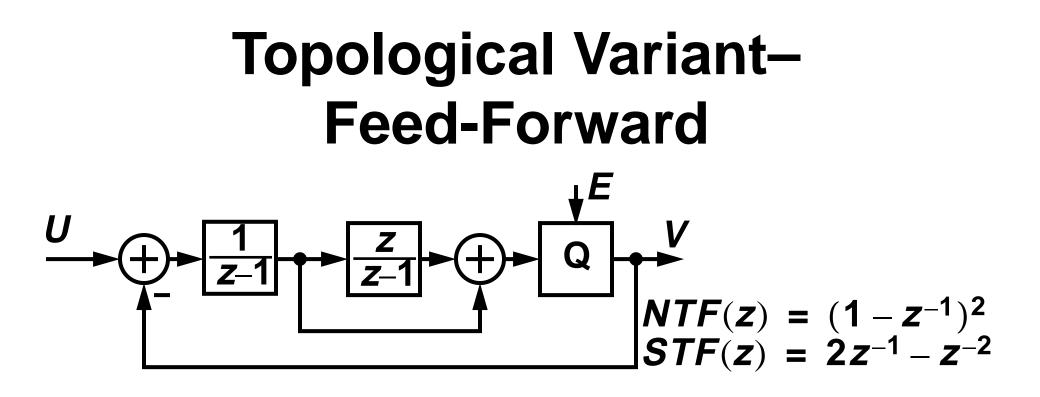

- Output of first integrator has no DC component

Dynamic range requirements of this integrator are relaxed.

- Although  $|STF| \approx 1$  near  $\omega = 0$ , |STF| = 3 for  $\omega = \pi$ Instability is more likely.

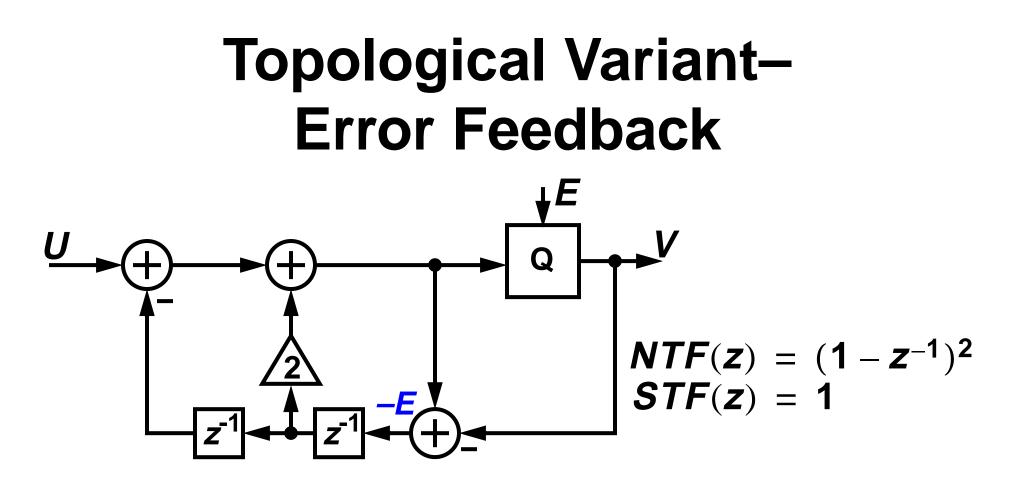

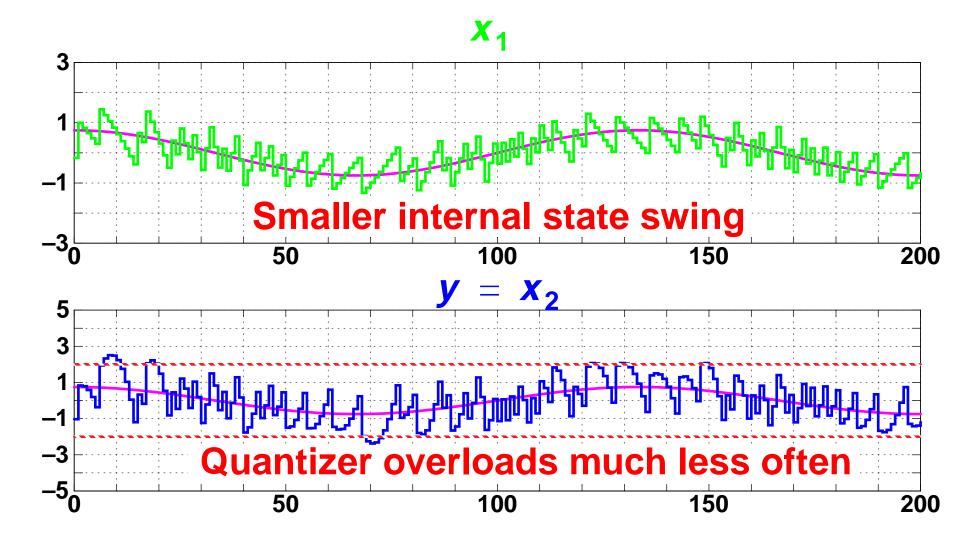

## **Topological Variant– Feed-Forward with Extra Feed-In**

- + No DC component in either integrator's output Reduced dynamic range requirements in both integrators, esp. for multi-bit modulators.

- + Perfectly flat STF No increased risk of instability.

- Timing is tricky

- + Simple

- Very sensitive to gain errors

Only suitable for digital implementations.

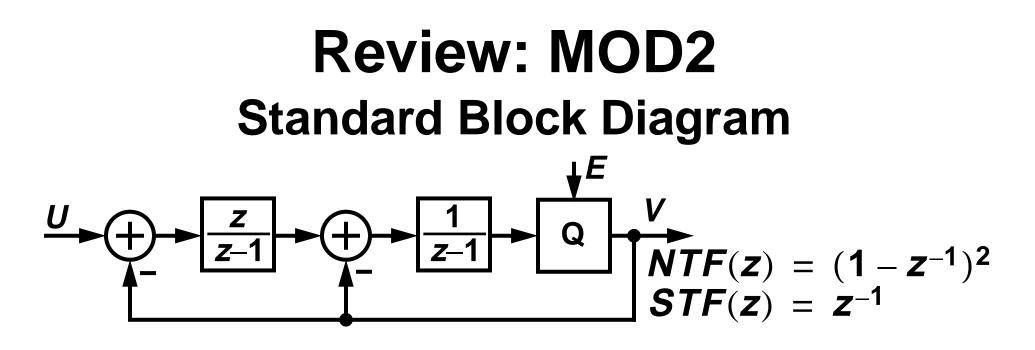

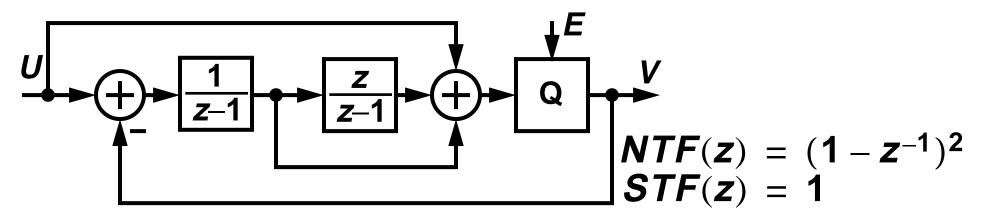

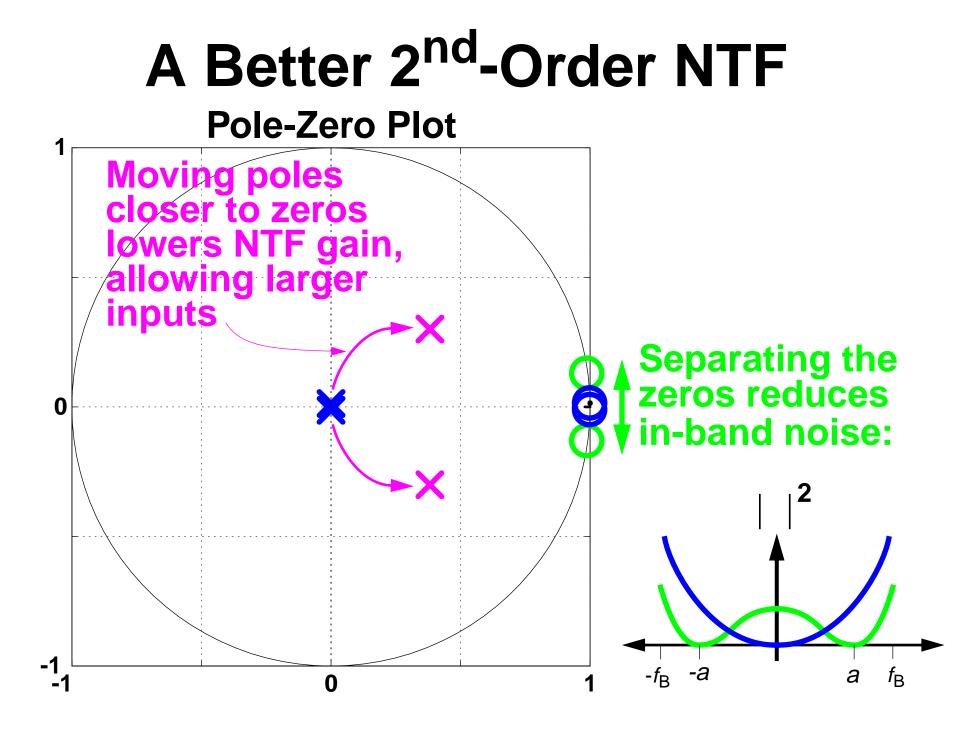

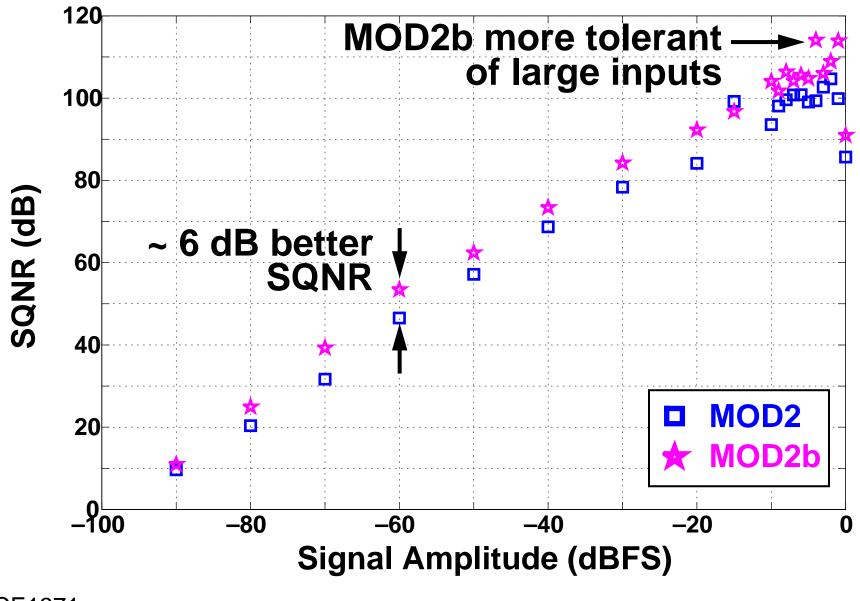

# Is MOD2 The Only 2<sup>nd</sup>-Order Modulator?

• Except for the filtering provided by the STF, any modulator with the same NTF as MOD2 has the same input-output behavior as MOD2

SQNR curve is the same.

Tonality of the quantization noise is unchanged.

- Internal states, sensitivity, thermal noise etc. can differ from realization to realization

- BUT, in terms of input-output behavior,

- A 2<sup>nd</sup>-order modulator is truly different only if it possesses a truly different (2<sup>nd</sup>-order) NTF

ECE1371

4-40

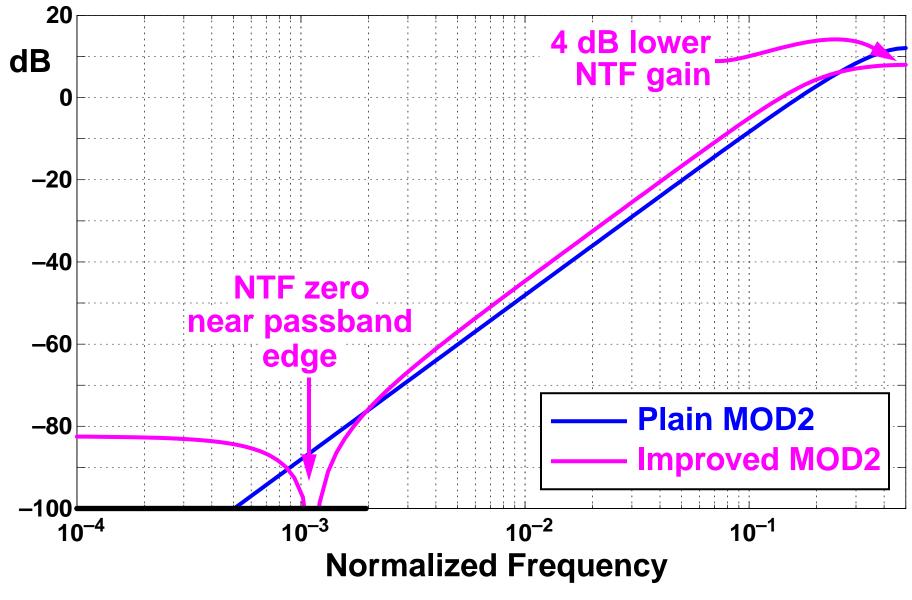

## **NTF Comparison**

## **SNR vs. Amp Comparison**

ECE1371

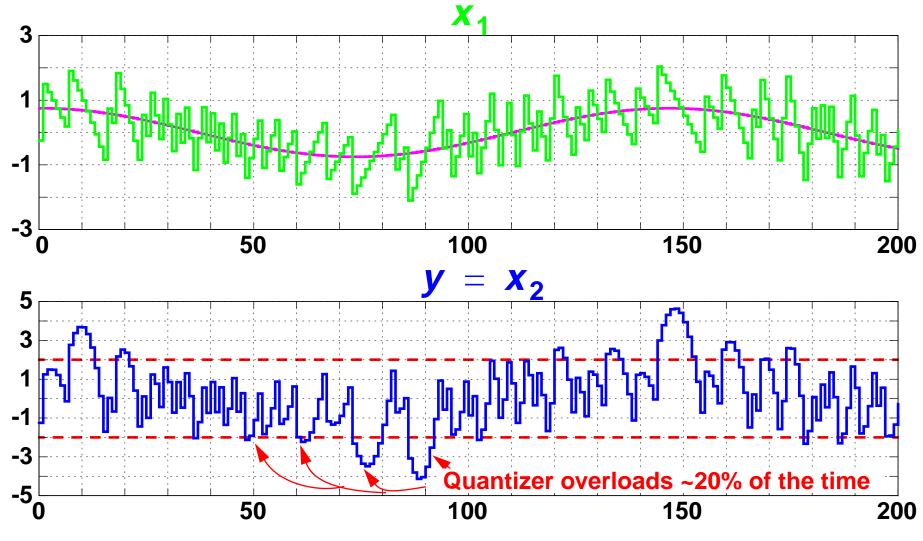

#### MOD2 Internal Waveforms Input @ 75% of FS

ECE1371

4-43

#### MOD2b Internal Waveforms Input @ 75% of FS

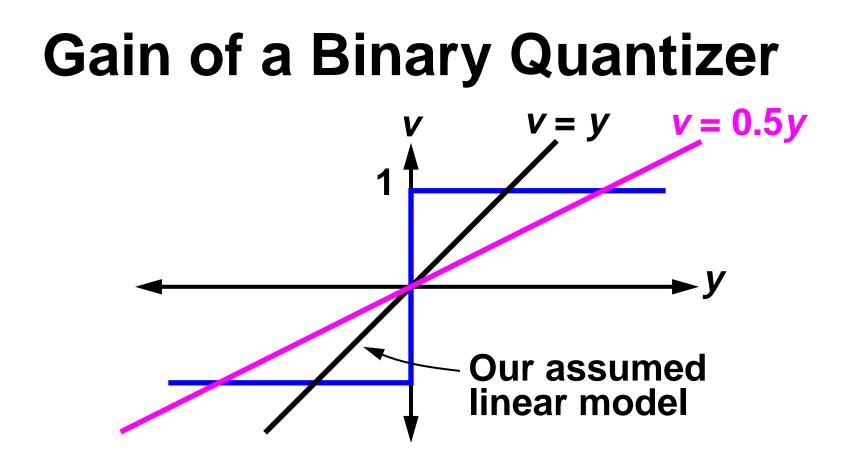

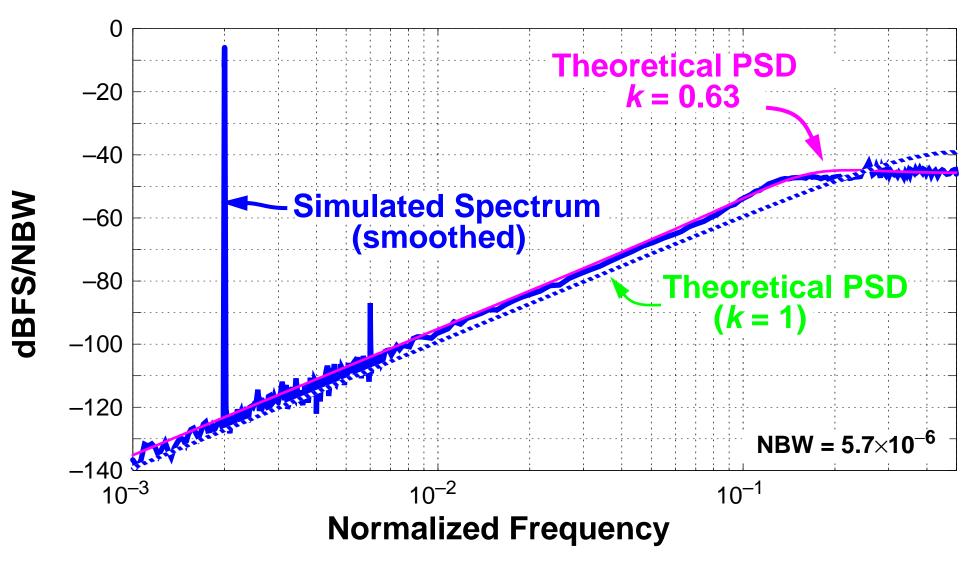

- The effective gain of a binary quantizer is not known a priori

- The gain (k) depends on the statistics of the quantizer's input

Halving the signal doubles the gain.

## Gain of the Quantizer in MOD2

• The effective gain of a binary quantizer can be computed from the simulation data using

$$k = \frac{E[|y|]}{E[y^2]}$$

[S&T Eq. 2.5]

• For the simulation of 2-14, k = 0.63

#### **Revised PSD Prediction**

• Agreement is now excellent

ECE1371

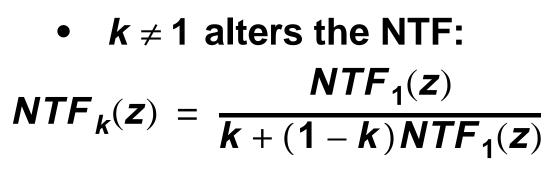

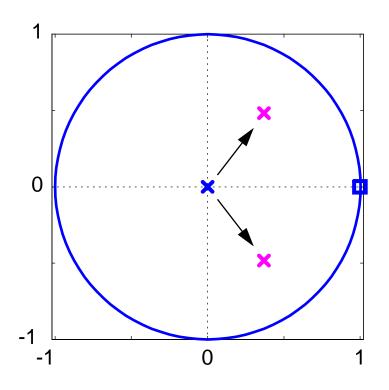

## Variable Quantizer Gain

- When the input is small (below –12 dBFS), the effective gain of MOD2's quantizer is *k* = 0.75

- MOD2's "small-signal NTF" is thus  $NTF(z) = \frac{(z-1)^2}{z^2 - 0.5z + 0.25}$

- This NTF has 2.5 dB less quantization noise suppression than the  $(1 z^{-1})^2$  NTF derived from the assumption that k = 1

Thus the SQNR should be about 2.5 dB lower than  $\times$ .

• As the input signal increases, *k* decreases and the suppression of quantization noise degrades SQNR increases less quickly than the signal power. Eventually the SQNR saturates and then decreases as the signal power reaches full-scale.

## What You Learned Today

- 1 Transistor-level implementation of MOD2 op-amp, SC CMFB, comparator, clock generator

- 2 MOD2 variants

- 3 Variable quantizer gain

#### Op Amp Gain Requirement Nonlinear Theory 1

• MOD2 has a "deadband" around u = 0 whose width is approximately

$$\frac{0.5(a_1c_1) + a_2}{A^2} = \frac{0.5((1/3) \cdot (1/3)) + (1/9)}{A^2} = \frac{1}{6A^2}$$

- To make the deadband less than 1 "LSB" wide,  $\frac{1}{6A^2} < \text{undbv}(-100) = 10^{-5},$ or A > 400 = 52 dB

- Since we didn't need so much gain to get excellent AC performance, this calculation looks like it is conservative

#### Op Amp Gain Requirements Nonlinear Theory 2

- Finite DC gain  $\Rightarrow$  incomplete charge transfer

- The gain is a nonlinear function, so the residual charge is nonlinearly related to the output voltage of the amplifier The residual charge is akin to noise.

- However, if the amplifier output contains signal components, then nonlinear gain can result in harmonic distortion

The feedforward topology is known to yield low distortion even when the amplifier gain is low.

• The effects are difficult to quantify analytically, and so we typically rely on simulations