ECE1371 Advanced Analog Circuits Lecture 7

# SWITCHED CAPACITOR CIRCUITS

Richard Schreier richard.schreier@analog.com

Trevor Caldwell trevor.caldwell@utoronto.ca

#### **Course Goals**

Deepen Understanding of CMOS analog circuit design through a top-down study of a modern analog system

The lectures will focus on Delta-Sigma ADCs, but you may do your project on another analog system.

Develop circuit insight through brief peeks at some nifty little circuits

The circuit world is filled with many little gems that

every competent designer ought to recognize.

ECE1371

7-2

|             |                           |    |                           |                    | 1                |

|-------------|---------------------------|----|---------------------------|--------------------|------------------|

| Date        | Lecture                   |    |                           | Ref                | Homework         |

| 2008-01-07  | RS                        | 1  | Introduction: MOD1 & MOD2 | S&T 2-3, A         | Matlab MOD2      |

| 2008-01-14  | RS                        | 2  | Example Design: Part 1    | S&T 9.1, J&M 10    | Switch-level sim |

| 2008-01-21  | RS                        | 3  | Example Design: Part 2    | J&M 14, S&T B      | Q-level sim      |

| 2008-01-28  | тс                        | 4  | Pipeline and SAR ADCs     | J&M 11,13          | Pipeline DNL     |

| 2008-02-04  | ISSCC – No Lecture        |    |                           |                    |                  |

| 2008-02-11  | RS                        | 5  | Advanced ΔΣ               | S&T 4, 6.6, 9.4, B | CTMOD2; Proj.    |

| 2008-02-18  | Reading Week – No Lecture |    |                           |                    |                  |

| 2008-02-25  | RS                        | 6  | Comparator and Flash ADC  | J&M 7              |                  |

| 2008-03-03  | тс                        | 7  | SC Circuits               | Raz 12, J&M 10     |                  |

| 2008-03-10  | тс                        | 8  | Amplifier Design          |                    |                  |

| 2008-03-17  | тс                        | 9  | Amplifier Design          |                    |                  |

| 2008-03-24  | тс                        | 10 | Noise in SC Circuits      | S&T C              |                  |

| 2008-03-31  | Project Presentations     |    |                           |                    |                  |

| 2008-04-07  | тс                        | 11 | Matching & MM-Shaping     |                    |                  |

| 2008-04-14  | RS                        | 12 | Switching Regulator       |                    | Project Report   |

| ECE1371 7-3 |                           |    |                           |                    |                  |

## **NLCOTD: Schmitt Trigger**

Problem: Input is noisy or slowly varying

How do we turn this into a clean digital output?

ECE1371

7-4

#### Highlights (i.e. What you will learn today)

- 1. Motivation for SC Circuits

- 2. Basic sampling switch and charge injection errors

- 3. Fundamental SC Circuits Sample & Hold, Gain and Integrator

- 4. Other Circuits Bootstrapping, SC CMFB

ECE1371

# Why Switched Capacitor?

- Used in discrete-time or sampled-data circuits

Alternative to continuous-time circuits

- Capacitors instead of resistors

Capacitors won't reduce the gain of high output

impedance OTAs

No need for low output impedance buffer to drive

resistors

- Accurate frequency response

Filter coefficients determined by capacitor ratios

(rather than RC time constants) and clock frequencies

Capacitor matching on the order of 0.1% when the

transfer characteristics are a function of only a

capacitor ratio, it can be very accurate

RC time constants vary by up to 20%

ECE1371

#### **Basic Building Blocks**

- Opamps

- Ideal usually assumed

Some important non-idealities to consider include:

- 1. DC Gain: sets the accuracy of the charge transfer, how 'grounded' the virtual ground is

- 2. Unity-gain freq, Phase Margin & Slew Rate: determines maximum clock frequency

- 3. DC Offsets: circuit techniques to combat this and 1/f noise - Correlated Double Sampling, Chopping

- Capacitors •

Large absolute variation, good matching Large bottom plate capacitor adds parasitic cap

ECE1371

7-7

## **Basic Building Blocks**

Switches

MOSFET switches are good - large off resistance (G $\Omega$ ), small on resistance (100 $\Omega$  - 5k $\Omega$ , depending on transistor sizing) MOSFET switches have non-linear parasitic capacitors

Non-Overlapping Clocks

Clocks are never on at the same time Required so that charge is never lost/shared

**Clock Generator previously discussed** ECE1371

7-8

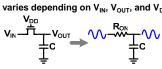

# **Basic Sampling Switch**

• MOSFET used as sample-and-hold When CLK is HIGH,  $V_{\text{OUT}}$  follows  $V_{\text{IN}}$  through the lowpass filter created by  $R_{\mbox{\scriptsize ON}}$  and C

$R_{\text{ON}}$  varies depending on  $V_{\text{IN}}, V_{\text{OUT}},$  and  $V_{\text{DD}}$

When CLK is LOW,  $V_{\mbox{\scriptsize OUT}}$  holds the value on C

ECE1371

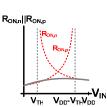

# **On-Resistance Variation**

• With an NMOS sampling switch, as VIN approaches  $V_{\text{DD}}\text{-}V_{\text{TH}},\,R_{\text{ON}}$  increases dramatically In smaller technologies, as  $V_{\text{DD}}$  decreases the swing on V<sub>IN</sub> is severely limited Ron

$$R_{ON} = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{DD} - V_{IN} - V_{TH})}$$

Sampling switch must be sized for worst case R<sub>ON</sub> so that the bandwidth is still sufficient

ECE1371

7-10

## **On-Resistance Variation**

- · PMOS switches suffer from the same problem as  $V_{IN}$  approaches  $V_T$

- · Complementary switch can allow rail-to-rail input swings

Ignoring variation of  $V_{TH}$  with  $V_{IN}$ ,  $R_{ON,eq}$  is constant with  $V_{IN}$  if  $\mu_n \mathbf{C}_{ox} \frac{W}{L} = \mu_p \mathbf{C}_{ox} \frac{W}{L}$

- Two situations to consider

- 1) Discrete-time signal When analyzing a signal within the switchedcapacitor circuit (for example, at the output of the first OTA)

#### 2) Continuous-time signal

When analyzing a signal that is sampled at the input

ECE1371

7-11

7-9

ECE1371

#### Settling Accuracy – DT

Discrete-Time Signal Settling Error = e<sup>-T/4RC</sup>

For N-bit accuracy in T/4 seconds  $R_{oN}C < \frac{T}{4N\ln 2}$

This is the maximum R<sub>oN</sub> (for a given C)

- Example:

- Assume 1 GHz to 4 GHz variation of  $\frac{1}{2\pi R_{ov}C}$

Input sinusoidal signal at 50 MHz  $2\pi R_{ov}$ For f<sub>s</sub>=100MHz, N=22 bits with discrete-time signal (typically you are limited by the OTA)

ECE1371

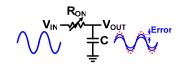

# Settling Accuracy – CT

Continuous-Time Signal

$R_{ON}C$  acts as a low-pass filter and introduces amplitude and phase change Variations in the input signal size cause variations in  $R_{ON}$ , causing distortion in the sampled signal Both the amplitude and phase vary – which one causes distortion?

```

ECE1371

```

ECE1371

7-14

# **Amplitude Error**

Less significant error

Due to variation in magnitude of low-pass filter

At 50 MHz (with same R<sub>ON</sub>C variation as DT case),

maximum possible error is 0.1%

ECE1371

7-15

7-13

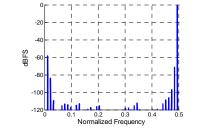

# Distortion in sampled CT input

Input ~50 MHz, sampled at 100MHz Distortion at 57dB, or ~9 bits This is larger than the maximum possible error due to amplitude variation

7-16

## **Phase Error**

• More significant error

Due to variation in phase of low-pass filter At 50 MHz (with same  $R_{\rm ON}C$  variation as DT case), maximum possible error is a few percent - error is less than that

#

#### ECE1371

7-17

# **Charge Injection**

- When a transistor turns off, the channel charge  $\mathbf{Q}_{\text{CH}}$  goes into the circuit

- Doesn't exactly divide in half depends on impedance seen at each terminal and the clock transition time  $Q_{CH} = WLC_{ox}(V_{DD} - V_{IN} - V_{TH})$

- Charge into V<sub>IN</sub> has no impact on output node Doesn't create error in the circuit

- Charge into C causes error ∆V in V<sub>OUT</sub>

$$\mathbf{V}_{\text{IN}} \underbrace{\frac{\mathbf{v}_{\text{CH}}}{\mathbf{v}_{\text{CH}}}}_{\mathbf{v}_{\text{CH}}} \underbrace{\mathbf{v}_{\text{CH}}}_{\mathbf{v}_{\text{C}}} \underbrace{\mathbf{v}_{\text{CH}}}_{\mathbf{v}_{\text{C}}} \mathbf{v}_{\text{OUT}} \qquad \Delta V = \frac{\mathbf{Q}_{\text{CH}}}{2C} \\ = \frac{WLC_{\text{ox}}(V_{\text{DD}} - V_{\text{IN}} - V_{\text{TH}})}{2C}$$

ECE1371

#### **Charge Injection**

In previous analysis, charge injection introduces a gain and offset error

This is still lines and outld be talented as a

This is still linear and could be tolerated or corrected

$$V_{OUT} = V_{IN} - \Delta V$$

=  $V_{IN} \left( 1 + \frac{WLC_{ox}}{2C} \right) - \frac{WLC_{ox}(V_{DD} - V_{TH})}{2C}$

• But...

$V_{TH}$  is actually a function of ~  $\sqrt{V_{IN}}$  Introduces non-linear term that cannot be corrected in the circuit

ECE1371

7-19

## **Charge Injection vs. Speed**

- Charge injection

Proportional to transistor size (WL)

- Speed R<sub>oN</sub> inversely proportional to aspect ratio (W/L)

- Figure of Merit Product of speed (1/ $\tau$ ) and charge injection (1/ $\Delta$ V)

$$(z\Delta V)^{-1} = \left(\frac{C}{\mu_n C_{ox}(W/L)(V_{DD} - V_{IN} - V_{TH})}\right)^{-1} \left(\frac{WLC_{ox}}{C}(V_{DD} - V_{IN} - V_{TH})\right)^{-1}$$

$$= \frac{\mu_n}{L^2}$$

ECE1371

7-20

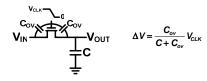

## **Clock Feedthrough**

Overlap capacitance allows clock to couple from the gate to drain/source terminals Change in voltage ∆V independent of the input signal Error is an offset voltage which is cancelled with differential operation

ECE1371

7-21

7-23

# **Charge Error Cancellation**

Differential operation

Cancels offset errors, depending on the matching

between differential circuits

Applies to signal dependent portion of charge

injection error, and clock feedthrough error

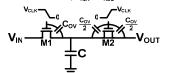

#### Complementary Switches

Error cancelled for 1 input level  $W_n L_n C_{ox}(V_{CLK} - V_{N} - V_{THN}) = W_p L_p C_{ox}(V_{IN} - |V_{THP}|)$ Clock feedthrough cancelled depending on similarity of overlap capacitance for PMOS and NMOS switches

ECE1371

7-22

# **Charge Error Cancellation**

• Dummy Switch

Use second transistor to remove charge injection by main transistor

Inverted clock operates on dummy switch Charge from M1:  $q_{M1} = W_{L}L_{C_{0X}}(V_{CK} - V_{N} - V_{TH1})/2$ Charge from M2:  $q_{M2} = W_{2}L_{2}C_{0X}(V_{CK} - V_{N} - V_{TH2})$ If charge splits equally in M1 (not quite true), then with M2 half the size of M1,  $q_{M1} = q_{M2}$

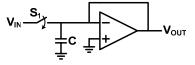

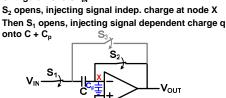

# Sample and Hold Amplifier

Input dependent charge from S<sub>1</sub> onto C When S1 turns off, charge q adds to C V<sub>OUT</sub> is then equal to V<sub>IN</sub>+q/C where q has a non-linear dependence on V<sub>IN</sub>

We can improve on this by making  $V_{\text{out}}$  independent of sampling switch charge...

ECE1371

7-24

ECE1371

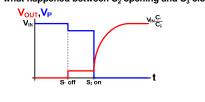

#### S/H Amplifier

- · Two phases

- Phase 1:  $S_1$  and  $S_2$  closed,  $V_{IN}$  sampled on C Phase 2:  $S_3$  closed, C is tied to  $V_{OUT}$

- Phase 1

- Charge on C is CV<sub>IN</sub>

ECE1371

7-25

#### S/H Amplifier

Phase 2

Node X is a virtual ground and charge on  $\mathbf{C}_{\mathbf{p}}$  is zero Charge on C is still  $\mathbf{CV}_{\mathbf{IN}}$

$S^{}_1$  /  $S^{}_3$  are non-overlapping,  $S^{}_2$  slightly ahead of  $S^{}_1_{\rm ECE1371}$

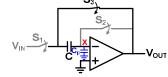

Gain of the S/H

Finite OTA gain reduces gain of sampler On Phase 1, C charges to V<sub>IN</sub> On Phase 2, node X goes from 0 to V<sub>x</sub> = -V<sub>OUT</sub>/A Charge comes from C, changing q<sub>C</sub> to CV<sub>IN</sub> + C<sub>p</sub>V<sub>x</sub> V<sub>OUT</sub> - (CV<sub>IN</sub> + C<sub>p</sub>V<sub>x</sub>)/C = V<sub>x</sub>

ECE1371

# Speed of the S/H

- In sampling mode (Phase 1) At node X,  $R_x \sim 1/G_m$ ,  $\tau_1 \sim (R_{on1}+1/G_m)C$

- In amplification mode (Phase 2) Replace charge on C by voltage source V<sub>IN</sub> (like switching in voltage source at start of Phase 2) After analysis, τ<sub>2</sub> = (C<sub>L</sub>C<sub>p</sub>+C<sub>p</sub>C+CC<sub>L</sub>)/G<sub>M</sub>C Reduces to τ<sub>2</sub> ~ C<sub>L</sub>/G<sub>M</sub> if C<sub>p</sub> is small

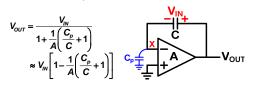

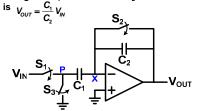

**Basic Amplifier**

- Sampling phase when S<sub>1</sub> and S<sub>2</sub> closed Input signal sampled onto C<sub>1</sub>

- Amplifying phase when S<sub>3</sub> closed Charge on C<sub>1</sub> transferred to C<sub>2</sub> so that the final output

7-29

ECE1371

7-27

# **Basic Amplifier**

- S<sub>2</sub> must open before S<sub>1</sub> for the charge injection to be signal independent

- Charge from  $\mathsf{S}_2$  opening is deposited on  $\mathsf{C}_1,$  but is not signal dependent

Charge from S<sub>1</sub> opening causes glitch in V<sub>OUT</sub> When S<sub>3</sub> closes, V<sub>OUT</sub> goes to final value, regardless of what happened between S<sub>2</sub> opening and S<sub>3</sub> closing

7-30

ECE1371

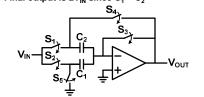

#### **Precision Gain-2**

- Sampling phase when S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub> closed Input signal sampled onto C<sub>1</sub> and C<sub>2</sub>

- Amplifying phase when S<sub>4</sub>, S<sub>5</sub> closed Charge on C<sub>1</sub> is transferred to C<sub>2</sub>, doubling the charge on C<sub>2</sub>

Final output is 2V<sub>IN</sub> since C<sub>1</sub> = C<sub>2</sub>

ECE1371

#### **Precision Gain-2**

• How is it more precise?

The feedback factor in both gain circuits is

$$\frac{C_2}{C_2 + C_1 + C_p}$$

In the precision Gain-2 circuit,  $C_1 = C_2$ , while the basic amplifier has  $C_1 = 2C_2$ , resulting in a smaller feedback factor and a slower circuit

The gain error is inversely proportional to the feedback factor, so the precision circuit is more accurate for a given amplifier gain A

$$\frac{V_{OUT}}{V_{IN}} \approx 2 \left( 1 - \frac{C_2 + C_1 + C_p}{AC_2} \right)$$

ECE1371

7-31

7-33

7-35

7-32

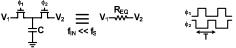

Average current through switched-capacitor

$$\phi_{1}: Q_{1} = CV_{1} \quad \phi_{2}: Q_{2} = CV_{2}$$

$$I_{AVG} = \frac{Q_{1} - Q_{2}}{T} = \frac{C(V_{1} - V_{2})}{T}$$

Equivalent current through a resistor (f<sub>IN</sub> << f<sub>S</sub>)

$$I_{EQ} = \frac{V_{1} - V_{2}}{R_{EQ}}$$

$R_{EQ} = \frac{T}{C} = \frac{1}{Cf_{c}}$

ECE1371

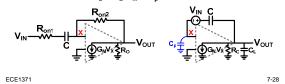

Switched-Capacitor Integrator

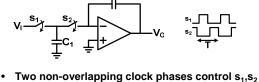

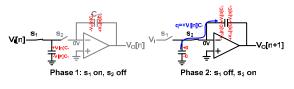

Two non-overlapping clock phases control s<sub>1</sub>,s<sub>2</sub> Phase 1: Sampling phase – input is sampled onto capacitor C<sub>1</sub> Phase 2: Integrating phase – additional charge is added to previous charge on C<sub>2</sub>

ECE1371

7-34

# **Switched-Capacitor Integrator**

• Final charge on L.S. of C2 is  $+V_0[n+1]C_2$  $+V_0[n+1]C_2 = +V_0[n]C_2 = V(n)C_2$

$$-V_{O}[n+1]C_{2} = +V_{O}[n]C_{2} - V_{I}[n]C_{1}$$

$$zV_{O}(z)C_{2} = V_{O}(z)C_{2} - V_{I}(z)C_{1}$$

$$\frac{V_{O}}{V_{I}}(z) = -\frac{C_{1}}{C_{2}}\frac{1}{z-1}$$

ECE1371

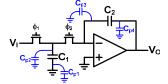

- Parasitic capacitances  $\mathbf{C}_{p1}, \, \mathbf{C}_{p3}$  and  $\mathbf{C}_{p4}$  have no impact on transfer function

- C<sub>p2</sub> in parallel with C<sub>1</sub>, changes transfer function

$$\frac{V_{o}}{V_{i}}(z) = -\frac{(C_{1}+C_{p2})}{C_{2}}\frac{1}{z-1}$$

ECE1371

#### **Parasitic Insensitive**

· Transfer function is non-inverting, delaying

$$\frac{V_0}{V_1}(z) = \frac{C_1}{C_2} \frac{1}{z - 1}$$

ECE1371

7-37

7-39

# Parasitic Insensitive

- Parasitics have no impact on transfer function Better linearity since non-linear capacitors are unimportant

- Top plate on virtual ground node Minimizes parasitics, improves amplifier speed and resolution, reduces noise coupled to node

- Two extra switches needed

More power to drive the switches for the same on resistance

ECE1371

7-38

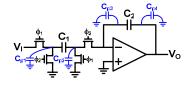

#### **Delay-Free Integrator**

- · Same structure, still parasitic insensitive

- Transfer function is inverting, delay-free

$$\frac{V_0}{V_1}(z) = -\frac{C_1}{C_2}\frac{z}{z-1}$$

ECE1371

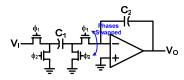

# **Bootstrapped Circuit**

Basic operation

#### Bootstrapping

- At low supply voltages, signal swing is limited Maximum distortion determines the tolerable variation in  $R_{\text{ON}}$ , and this limits the signal swing

- Want to increase V<sub>GS</sub> on the sampling switch Can do this by increasing the supply voltage for the sampling switch, but this requires slower thick oxide devices

Alternatively, add a constant voltage to the input signal and use that as the gate voltage – keep  $V_{\rm GS}$  constant, reducing the variation in  $R_{\rm ON}$

ECE1371

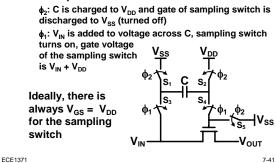

## **Bootstrapped Circuit**

C must be sized so that charge sharing between gate capacitance of switch is not significant

$$V_{G} = V_{IN} + \frac{C}{C + C_{G}} V_{DD}$$

- Rise time controlled by size of S<sub>4</sub>, fall time controlled by size of S<sub>5</sub>

- Extra transistors required to limit gate-source voltages to V<sub>DD</sub> and prevent overstress See Dessouky, JSSC Mar.2001

ECE1371

7-42

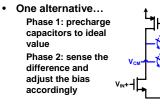

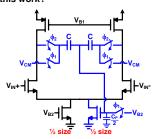

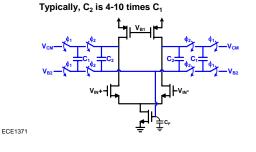

# Switched-Capacitor CMFB

· Two parts to the circuit

First, sense the common mode of the output Second, compare the common mode to the expected common mode, and adjust the bias accordingly

Sensing

Could use 2 resistors - they are either too small and reduce the gain, or they can get prohibitively large Could use 2 capacitors - they don't reduce the gain, but the voltage across them is undefined The voltage across them can be refreshed every clock cycle

ECE1371

7-43

7-45

## **Switched-Capacitor CMFB**

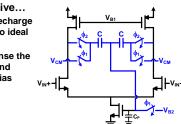

But... there may be large changes in the tail current bias

ECE1371

7-44

# **Switched-Capacitor CMFB**

· Solution: Part of the tail current source can be controlled by a constant bias voltage Will this work?

ECE1371

# **NLCOTD: Schmitt Trigger**

# **Switched-Capacitor CMFB**

· Alternatively, use 2 capacitors so that only a fraction of the charge is shared to adjust the bias voltage

## What You Learned Today

- 1. Errors introduced with simple sampling switch RON variation, charge injection

- 2. Main SC Circuits S/H, Gain and Integrators Parasitic Insensitive Signal-independent charge injection

- 3. Bootstrapped Circuit

- 4. Switched Capacitor CMFB

7-47

ECE1371

7-48