## ECE1371 Advanced Analog Circuits Lecture 8

#### **AMPLIFIER DESIGN**

Richard Schreier richard.schreier@analog.com

Trevor Caldwell trevor.caldwell@utoronto.ca

#### **Course Goals**

Deepen Understanding of CMOS analog circuit design through a top-down study of a modern analog system

The lectures will focus on Delta-Sigma ADCs, but you may do your project on another analog system.

Develop circuit insight through brief peeks at some nifty little circuits

The circuit world is filled with many little gems that every competent designer ought to recognize.

| Date       | Lecture                   |                       |                           | Ref                | Homework         |  |  |  |

|------------|---------------------------|-----------------------|---------------------------|--------------------|------------------|--|--|--|

| 2008-01-07 | RS                        | 1                     | Introduction: MOD1 & MOD2 | S&T 2-3, A         | Matlab MOD2      |  |  |  |

| 2008-01-14 | RS                        | 2                     | Example Design: Part 1    | S&T 9.1, J&M 10    | Switch-level sim |  |  |  |

| 2008-01-21 | RS                        | 3                     | Example Design: Part 2    | J&M 14, S&T B      | Q-level sim      |  |  |  |

| 2008-01-28 | тс                        | 4                     | Pipeline and SAR ADCs     | J&M 11,13          | Pipeline DNL     |  |  |  |

| 2008-02-04 | ISSCC - No Lecture        |                       |                           |                    |                  |  |  |  |

| 2008-02-11 | RS                        | 5                     | Advanced ΔΣ               | S&T 4, 6.6, 9.4, B | CTMOD2; Proj.    |  |  |  |

| 2008-02-18 | Reading Week – No Lecture |                       |                           |                    |                  |  |  |  |

| 2008-02-25 | RS                        | 6                     | Comparator and Flash ADC  | J&M 7              |                  |  |  |  |

| 2008-03-03 | тс                        | 7                     | SC Circuits               | Raz 12, J&M 10     |                  |  |  |  |

| 2008-03-10 | тс                        | 8                     | Amplifier Design          |                    |                  |  |  |  |

| 2008-03-17 | тс                        | 9                     | Amplifier Design          |                    |                  |  |  |  |

| 2008-03-24 | тс                        | 10                    | Noise in SC Circuits      | S&T C              |                  |  |  |  |

| 2008-03-31 | RS                        | 11                    | Switching Regulator       |                    |                  |  |  |  |

| 2008-04-07 |                           | Project Presentations |                           |                    |                  |  |  |  |

| 2008-04-14 | TC                        | 12                    | Matching & MM-Shaping     | _                  | Project Report   |  |  |  |

ECE1371 8-3

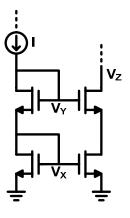

# NLCOTD: Wide-Swing Cascode Current Mirror

- How do we bias cascode transistors to optimize signal swing?

- Standard cascode current mirror wastes too much swing

$$\begin{split} &V_X = V_{EFF} + V_T \\ &V_Y = 2V_{EFF} + 2V_T \\ &\text{Minimum } V_Z \text{ is } 2V_{EFF} + V_T, \\ &\text{which is } V_T \text{larger than} \\ &\text{necessary} \end{split}$$

#### **Highlights**

#### (i.e. What you will learn today)

- 1. Choice of V<sub>EFF</sub>

Several trade-offs with Noise, Bandwidth, Power,...

- 2. Amplifier Topology

- 3. Amplifier Settling

Dominant Pole, Zero and Non-Dominant Pole

- 4. Gain-Boosting

Stability, Pole-Zero Doublet

- 5. Delaying vs. Non-Delaying stages

ECE1371 8-5

#### **Choice of Effective Voltage**

Effective Voltage V<sub>EFF</sub> = V<sub>GS</sub> - V<sub>T</sub>

$$V_{\text{EFF}} = \frac{2I_{D}}{g_{\text{m}}} = \sqrt{\frac{2I_{D}}{\mu_{\text{n}}C_{\text{ox}}W_{L}'}}$$

Assumes square-law model

In weak-inversion, this relationship will not hold

What are the trade-offs when choosing an appropriate effective voltage?

Noise Power Bandwidth Swing

Matching

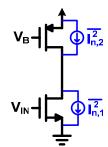

#### Thermal Noise and V<sub>FFF</sub>

Noise Current and Noise Voltage

$$\overline{I_n^2} = 4kT\gamma g_m \qquad \overline{V_n^2} = \frac{4kT\gamma}{g_m}$$

Ex. Common Source with transistor load

CS transistor has input referred noise voltage proportional to V<sub>EFF</sub>

$$\overline{V_n^2} = V_{EFF,1} \frac{4 k T \gamma}{2 I_D}$$

Current source has input referred noise voltage inversely proportional to  $\mathbf{V}_{\text{EFF}}$

$$\overline{V_n^2} = \frac{4 k T \gamma}{2 I_D} \frac{V_{EFF,1}^2}{V_{EFF,2}}$$

ECE1371 8-7

### Thermal Noise and V<sub>EFF</sub>

Total Noise

$$\overline{V_n^2} = \frac{4 k T \gamma}{2 I_D} V_{EFF,1} \left( 1 + \frac{V_{EFF,1}}{V_{EFF,2}} \right)$$

Use small  $\rm V_{\rm EFF}$  for input transistor, large  $\rm V_{\rm EFF}$  for load (current source) transistor

#### Bandwidth and V<sub>FFF</sub>

Bandwidth dependent on transistor unity gain frequency f<sub>T</sub>

$$f_{T} = \frac{g_{m}}{2\pi(C_{GS} + C_{GD})}$$

If C<sub>GS</sub> dominates capacitance

$$f_T \approx \frac{1.5\mu_n}{2\pi I^2} V_{EFF}$$

Small L, large  $\mu$  maximizes  $f_T$

For a given current, decreasing  $V_{\text{EFF}}$  increases W, increases  $C_{\text{GS}}$ , and slows down the transistor

• f<sub>T</sub> increases with V<sub>EFF</sub>

ECE1371 8-9

## Power and V<sub>EFF</sub>

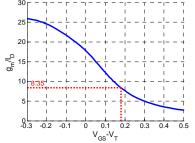

• Efficiency of a transistor is g<sub>m</sub>/l<sub>D</sub>

Transconductance for a given current – high efficiency results in lower power

Bipolar devices have  $g_m=I_C/V_t$ , while (square-law) MOS devices have  $g_m=2I_D/V_{EFF}$ ;  $V_{EFF}$  larger than  $V_t$

V<sub>EFF</sub> is inversely proportional to g<sub>m</sub>/I<sub>D</sub> Increasing V<sub>EFF</sub> reduces efficiency of the transiste

Increasing V<sub>EFF</sub> reduces efficiency of the transistor Biasing in weak inversion increases efficiency

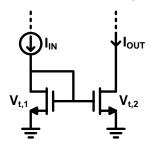

### Matching and V<sub>EFF</sub>

- With low V<sub>EFF</sub>, transistor is in weak inversion What happens with mismatch in V<sub>1</sub>?

- Use a current-mirror as an example with mismatched threshold voltages

ECE1371 8-11

#### Matching and V<sub>EFF</sub>

In strong inversion with V<sub>t</sub> mismatch there is a quadratic relationship

$$\frac{I_{OUT}}{I_{IN}} = \frac{(V_{GS} - V_{t,2})^2}{(V_{GS} - V_{t,1})^2}$$

1mV error in  $V_t$  is ~1% error in  $I_{OUT}$  (for  $V_{EFF}$ ~200mV)

In weak inversion with V<sub>t</sub> mismatch there is an exponential relationship

$$\frac{I_{OUT}}{I_{IN}} = \frac{e^{\frac{V_{GS} - V_{t,1}}{nV_T}}}{e^{\frac{V_{GS} - V_{t,2}}{nV_T}}} = e^{\frac{V_{t,2} - V_{t,1}}{nV_T}}$$

1mV error in V<sub>t</sub> is ~4% error in I<sub>OUT</sub>

### Swing and V<sub>EFF</sub>

Minimum V<sub>DS</sub> of a transistor to keep it in saturation is V<sub>FFF</sub>

Usually  $V_{DS}$  is  $V_{EFF}$  + 50mV or more to keep  $r_o$  high (keep the transistor in the saturation region) With limited supply voltages, the larger the  $V_{EFF}$ , the larger the  $V_{DS}$  across the transistor, less room for signal swing

Consequences

Can't cascode – reduced OTA gain

Stage gain is smaller – input referred noise is larger (effectively the SNR at the stage output is less)

ECE1371 8-13

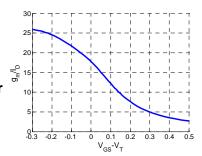

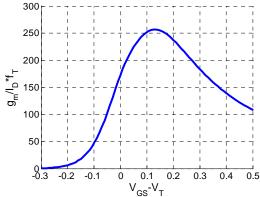

#### **Speed-Efficiency Product**

• What is the optimal  $V_{EFF}$  using a figure of merit defined as the product of  $f_T$  and  $g_m/I_D$ Optimal point at  $V_{EFF}$  = 130mV in 0.18 $\mu$ m

## **Summary of Trade-Offs**

Benefits of larger V<sub>EFF</sub>

Larger bandwidth

Better device matching

Lower input-referred noise for current-source

transistors

Benefits of smaller V<sub>EFF</sub>

Better efficiency – lower power

Larger signal swings

Better noise performance for input transistors

Good starting point:  $V_{EFF} \sim V_{DD}/10$

ECE1371 8-15

## **Device Parameter Summary**

| <b>Device Parameter</b> | Circuit Implications                                                                                                                                 |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>EFF</sub>        | Current Efficiency, g <sub>m</sub> /I <sub>D</sub> (matching) Power Dissipation Speed Cutoff Frequency, f <sub>T</sub> (phase margin) Noise Headroom |  |  |  |

| L                       | Cutoff Frequency, f <sub>T</sub> Intrinsic transistor gain                                                                                           |  |  |  |

| w                       | Obtain from L, I <sub>D</sub><br>Self Loading (C <sub>GS</sub> , C <sub>GD</sub> )                                                                   |  |  |  |

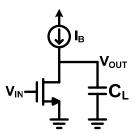

## **Common Source Design**

• Simple Design Example

Specs:  $C_L = 5pF$ ,  $f_u = 100MHz$ , Gain = 40

V<sub>EFF</sub>:

Assume we size it slightly higher than optimal  $f_T^*g_m/I_D$

$$V_{EFF} = 180 mV$$

$$\omega_{\rm U} = g_{\rm m}/C_{\rm L} = 2\pi 10^8$$

$g_{\rm m} = 3.14 {\rm mS}$

ECE1371 8-17

### **Common Source Design**

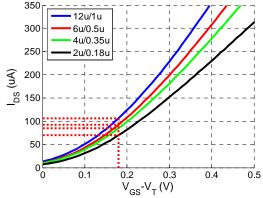

How do we find L for the desired gain?

Find current densities ( $V_{\text{EFF}}$ =180mV) for various L's Find the corresponding  $g_{\text{m}}r_{\text{o}}$  of these transistors

#### **Common Source Design**

How do we find L?

2u/0.18u @ 70uA: 23.5

4u/0.35u @ 85uA : 46.4 ← Choose for desired gain

6u/0.5u @ 93uA : 69.0 12u/1u @ 107uA : 114.9

I<sub>D</sub>:

$V_{EFF}$  and  $g_{m} => I_{D}$  $I_{D} = g_{m}/8.35 = 376uA$

ECE1371

ჾ-19

#### **Common Source Design**

W:

We have L and  $I_D$ 85uA for 4u/0.35u, we need 376uA W = 376uA/85uA\*4um = 4.4 x 4u/0.35u

2<sup>nd</sup> Pole:

$C_{GS}$  ~ 9fF\*4.4 = 40fF (1+A) $C_{GD}$  ~ 1.5fF\*4.4\*46 = 304fF With 50 $\Omega$  source resistance,  $\omega_{p2}$  ~ 9 GHz

#### **Amplifier Topology**

• Briefly... (covered in Analog I, from Razavi Ch.9)

| Topology           | Gain   | Output<br>Swing | Speed   | Power Dissipation | Noise  |

|--------------------|--------|-----------------|---------|-------------------|--------|

| Telescopic         | Medium | Medium          | Highest | Low               | Low    |

| Folded-<br>Cascode | Medium | Medium          | High    | Medium            | Medium |

| Two-Stage          | High   | Highest         | Low     | Medium            | Low    |

| Gain-<br>Boosted   | High   | Medium          | Medium  | High              | Medium |

ECE1371 8-21

#### **Amplifier Errors**

• Two errors: Dynamic and Static

Static Errors

Limit the final settling accuracy of the amplifier Capacitor Mismatch ( $C_1/C_2$  error)

Finite OTA gain

$$\frac{V_{o}}{V_{i}}(z) = \frac{C_{1}}{C_{2}} \left( \frac{\frac{C_{2}A}{C_{2}(1+A) + C_{1}}}{z - \frac{C_{2}(1+A) + C_{1}}{C_{2}(1+A) + C_{1}}} \right)$$

ECE1371

#### **Amplifier Errors**

Dynamic Errors: Occurs in the integration phase when a 'step' is applied to the OTA

**Slewing**

Finite bandwidth

Feedforward path

Non-dominant poles

ECE1371 8-23

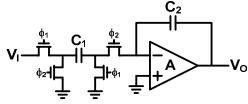

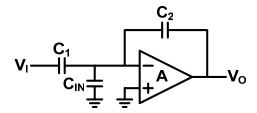

#### **Amplifier Errors**

First look at frequency independent response Static error term 1/Aβ

$$\frac{V_{0}}{V_{I}} = -\frac{C_{1}}{C_{2}} \frac{1}{1 + 1/A\beta} \approx -\frac{C_{1}}{C_{2}} \left( 1 - \frac{1}{A\beta} \right)$$

$$\beta = \frac{C_{2}}{C_{1} + C_{2} + C_{IN}}$$

• Example: 0.1% error at output

$$C_1 = 4pF$$

,  $C_2 = 1pF$ ,  $C_{IN} = 1pF$

$$\frac{V_O}{V_I} \approx -4\left(1 - \frac{6}{A}\right)$$

A > 6000 for 0.1% error

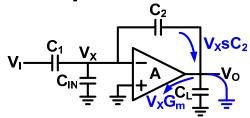

#### **Amplifier Errors**

What is the transfer function of this circuit?

By inspection...

Gain is -C<sub>1</sub>/C<sub>2</sub>

Zero when  $V_x s C_2 = V_x G_m$

Pole at  $\beta G_m/C_{L,eff}$  where  $C_{L,eff} = C_2(1-\beta) + C_L$

$$\frac{V_O}{V_I} = -\frac{C_1}{C_2} \frac{1 - \frac{sC_2}{G_m}}{1 + \frac{sC_{L,eff}}{\beta G_m}}$$

ECE1371

8-25

#### **Single-Pole Settling Error**

• Single-pole settling (ignore zero)

Step response of 1st-order (unity-gain) system

Unit step

$$\frac{1}{s}$$

through system  $\frac{1}{1+s/\beta\omega_{unity}}$

Inverse Laplace transform of

$$\frac{1}{s(1+s/\beta\omega_{unity})}$$

Step response is  $1 - e^{-\beta \omega_{unity}t}$

Error is

$$e^{-\beta \omega_{unity}t}$$

Settles to N-bit accuracy in

$$t > \frac{N \ln 2}{\beta \omega_{unitv}}$$

ECE1371

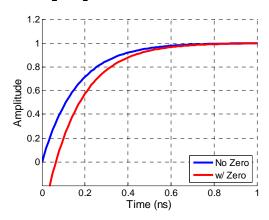

#### Pole and Zero Settling Error

Single-pole settling with feedforward zero

Step response, 1<sup>st</sup>-order system with feedforward zero

Unit step

$$\frac{1}{s}$$

through system  $\frac{1+s/\omega_z}{1+s/\beta\omega_{unity}}$

Inverse Laplace transform of  $\frac{1+s/\omega_z}{s(1+s/\beta\omega_{unity})}$

Step response is  $1-e^{-\beta\omega_{unity}t}+\frac{\beta\omega_{unity}}{\omega_z}e^{-\beta\omega_{unity}t}$

Error is  $e^{-\beta\omega_{unity}t}-\frac{\beta\omega_{unity}}{\omega_z}e^{-\beta\omega_{unity}t}$

Settles to N-bit accuracy in  $t>\frac{N\ln 2+\ln(1-\beta\omega_{unity}/\omega_z)}{\beta\omega_{unity}}$

ECE1371 8-2

#### **Effect of Zero on Settling**

Zero slows down settling time

Additional settling term

$$-\frac{\beta\omega_{unity}}{\omega_{z}}\,\mathbf{e}^{-\beta\omega_{unity}t}$$

Coefficient a function of feedback factor  $\beta$

$$-\frac{\beta \omega_{unity}}{\omega_z} = \frac{\beta G_m / C_{L,eff}}{G_m / C_2} = \frac{\beta C_2}{(1 - \beta)C_2 + C_L}$$

• To reduce impact of feedforward zero...

Smaller  $\beta$  (one of the few advantages of reducing  $\beta)$  Larger  $\textbf{C}_{\textbf{L}}$

#### **Effect of Zero on Settling**

• Example of settling behaviour

$$\beta = 1/2, C_L = C_2/2$$

ECE1371 8-29

### **Two-Pole Settling Error**

Dominant and non-dominant pole settling Step response, 2<sup>nd</sup>-order system

Unit step

$$\frac{1}{s}$$

through system  $\frac{1}{\omega_{p2} \cdot \beta \omega_{unity}} + \frac{s}{\beta \omega_{unity}} + 1$

Step response is dependent on relative values of  $\beta\omega_{\rm unity}$  and  $\omega_{\rm p2}$

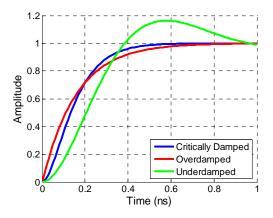

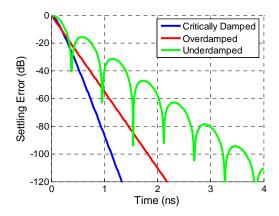

3 Cases:

Overdamped,  $\omega_{p2} > 4\beta\omega_{unity}$ Critically damped,  $\omega_{p2} = 4\beta\omega_{unity}$ Underdamped,  $\omega_{p2} < 4\beta\omega_{unity}$

#### **Two-Pole Settling Error**

• Overdamped,  $\omega_{p2} > 4\beta\omega_{unity}$

2<sup>nd</sup> pole much larger than unity-gain frequency Similar to 1<sup>st</sup>-order settling as 2<sup>nd</sup> pole approaches infinity

Step response is  $1 - \frac{B}{B - A} e^{-At} - \frac{A}{A - B} e^{-Bt}$

$$A, B = \frac{\omega_{p2}}{2} \pm \frac{\sqrt{\omega_{p2}^2 - 4\omega_{p2}\beta\omega_{unity}}}{2}$$

• Critically damped,  $\omega_{p2} = 4\beta\omega_{unity}$

No overshoot

Step response is  $1 - e^{-2\beta\omega_{unity}t} - 2\beta\omega_{unity}te^{-2\beta\omega_{unity}t}$

ECE1371 8-31

#### **Two-Pole Settling Error**

• Underdamped,  $\omega_{p2} < 4\beta\omega_{unity}$ Minimum settling time depending on desired SNR Increasing overshoot as  $\omega_{p2}$  decreases

Step response is

$$1 - e^{-\frac{\omega_{p2}}{2}t} \cos\left(t\sqrt{\beta\omega_{unity}\omega_{p2} - \frac{{\omega_{p2}}^2}{4}}\right) - \frac{e^{-\frac{\omega_{p2}}{2}t} \sin\left(t\sqrt{\beta\omega_{unity}\omega_{p2} - \frac{{\omega_{p2}}^2}{4}}\right)}{\sqrt{\frac{4\beta\omega_{unity}}{\omega_{p2}} - 1}}$$

## **Two-Pole Settling**

• Example:

$$\beta \omega_{unit}/2\pi = 1$$

GHz

$\omega_{p2}/2\pi = 1$ GHz, 4GHz, 100GHz

ECE1371

8-33

## **Two-Pole Settling**

Critically damped system settles faster than single-pole system

#### **Two-Pole Settling**

Underdamped system gives slightly better settling time depending on the desired SNR

ECE1371 8-35

#### **Two-Pole Settling**

For a two-pole system, phase margin can be used equivalently

$$PM = 90 - \frac{180}{\pi} \tan^{-1} \left( \frac{\omega_{p2}}{\omega_{unity}} \right)$$

Critically damped: PM = 76 degrees

**Underdamped: PM < 76 degrees**

(45 degrees if  $\omega_{p2} = \beta \omega_{unity}$ )

Overdamped: PM = 76 to 90 degrees

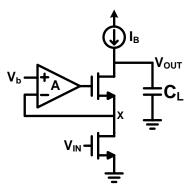

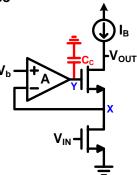

### **Gain-Boosting**

Increase output impedance of cascoded transistor

Impedance boosted by gain of amplifier A

$$V_{OUT}/V_{IN} = -g_m R_{OUT}$$

$R_{OUT} \sim Ag_m r_o^2$

Doesn't cost voltage headroom

Amplifier requires some power, but does not have to be very fast

ECE1371 8-37

#### **Gain-Boosting**

Need to analyze gain-boosting loop to ensure that it is stable

Cascade of amplifier A and source follower from node Y to node X

What is the load capacitance at node Y?

$$C_{GS}$$

? ~0.1 $C_{GS}$ ?

Node Y might be dominated by parasitic capacitances with large variations – use  $C_{\rm C}$  for a predictable response

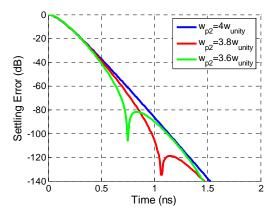

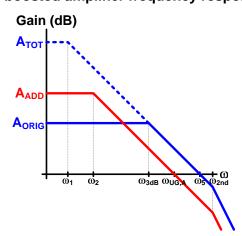

#### **Gain-Boosting**

Stability of gain-boosted amplifier

For 1<sup>st</sup>-order roll-off, the unity-gain frequency of the additional amplifier must be greater than the 3dB frequency of the original stage

$$\omega_{3dB} < \omega_{UG,A}$$

2<sup>nd</sup> pole of feedback loop is equivalent to 2<sup>nd</sup> pole of main amplifier

Set unity-gain frequency of additional amplifier lower than  $2^{nd}$  pole of main amplifier (or set it to  $\omega_{UG,A}$  ~  $\omega_{2nd}/3$  for a phase margin of ~71 degrees)

$$\omega_{\text{UG,A}} < \omega_{\text{2nd}}$$

ECE1371 8-39

#### **Gain-Boosting**

A<sub>ORIG</sub>: Original amplifier response without gain-boosting

A<sub>ADD</sub>: Frequency response of feedback amplifier A

A<sub>TOT</sub>: Gain-boosted amplifier frequency response

ECE1371

#### **Gain-Boosting**

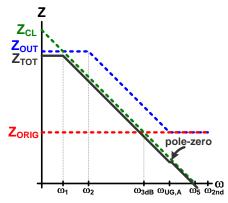

- Pole-zero doublet occurs at ω<sub>UG,A</sub>

Must ensure that this time constant does not dominate the settling behaviour

- Set  $\beta\omega_5$  (3dB frequency of closed loop amplifier response) below  $\omega_{\text{UG},A}$

Ensures that time constant is dominated by 3dB frequency and not the pole-zero doublet

$\beta\omega_5 < \omega_{UG,A}$

Final Constraint:  $\beta\omega_5 < \omega_{UG,A} < \omega_{2nd}$

ECE1371 8-41

#### **Pole-Zero Doublet**

**Z<sub>CL</sub>: Load Capacitance**

Z<sub>OUT</sub>: gain-boosted output impedance ~ (1+A)g<sub>m</sub>r<sub>o</sub><sup>2</sup>

$Z_{ORIG}$ : cascoded output impedance ~  $g_m r_o^2$

**Z**<sub>TOT</sub>: Total Output Impedance

ECE1371

#### **Pole-Zero Doublet**

Why is this a problem?

Doublet introduces a slower settling component in the step response

Step response (where  $\omega_z$  and  $\omega_p$  are the doublet pole and zero locations):

$$1 - e^{-\beta \omega_{unity}t} + \frac{\omega_z - \omega_\rho}{\beta \omega_{unity}} e^{-\omega_z t}$$

A higher-frequency doublet will always have an impact but will die away quickly

A lower-frequency doublet will not have as large an impact, but it will persist much longer

ECE1371 8-43

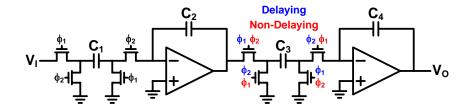

#### **Delaying vs. Non-Delaying Stage**

Depending on the architecture and stage sizing, this can be a large power penalty

Large C<sub>L</sub> greatly reduces the power efficiency of an amplifier

Amplifier must be larger, resulting in a smaller feedback factor and reduced bandwidth

#### **Delaying Stage**

#### Delaying

Subsequent stage does not load the output Very little C<sub>L</sub> on output of the amplifier

#### Example:

1<sup>st</sup> stage 4x larger than 2<sup>nd</sup> stage ( $C_3 = 0$  for delaying,  $C_3 = C_1/4$  for non-delaying) Each stage has gain of 2 ( $C_1/C_2 = 2$ ,  $C_3/C_4 = 2$ )

$$\begin{aligned} & \boldsymbol{C}_{L,eff} = \frac{\boldsymbol{C}_2(\boldsymbol{C}_1 + \boldsymbol{C}_{IN})}{\boldsymbol{C}_1 + \boldsymbol{C}_2 + \boldsymbol{C}_{IN}} + \boldsymbol{C}_3 = \beta(\boldsymbol{C}_1 + \boldsymbol{C}_{IN}) + \boldsymbol{C}_3 \\ & \boldsymbol{P}_{delay} \propto \beta \omega_{unity} = \frac{\beta \boldsymbol{g}_m}{\boldsymbol{C}_{L,eff}} = \frac{\boldsymbol{g}_m}{\boldsymbol{C}_1 + \boldsymbol{C}_{IN}} \end{aligned}$$

ECE1371 8-45

#### Non-Delaying Stage

#### Non-Delaying

Subsequent stage loads the output Applicable in pipeline ADCs, sometimes  $\Delta\Sigma$  (usually subsequent stages much smaller, depending on OSR) Opamp is wasted during the non-amplifying stage (could power it down to save power)

#### Example (continued):

$$\beta \omega_{unity} = \frac{\beta g_m}{C_{L,eff}} = \frac{g_m}{1.75C_1 + 1.5C_{IN}}$$

Increase  $g_m$  by 1.75 =>  $C_{IN}$  increases by 1.75 (approximately the same bandwidth with 1.75x power)

$$P_{non-delay} \propto 1.75 \beta \omega_{unity} = \frac{1.75 g_m}{1.75 C_1 + 2.6 C_{IN}}$$

#### **Amplifier Stability**

Both phases are important

Different loading on sampling and amplification phase

Feedback factor is larger in sampling phase than amplification phase

Amplifier could potentially go unstable if it was originally sized for optimal phase margin in the amplification mode

Non-Delaying stages are more susceptible to instability in sampling phase since a much smaller load capacitance is present

ECE1371 8-47

#### **Amplifier Stability**

Example:

$C_1 = 2pF, C_2 = 1pF, C_{IN} = 1pF$

$C_L = 0.5pF$  (load of subsequent stage)

**Delaying Stage**

Amplification:  $\beta \omega_{unity} = g_m/3pF$

Sampling:  $\beta = 1/2$ ,  $C_{L.eff} = 1pF$ ,  $\beta \omega_{unitv} = g_m/2pF$

Phase Margin: 73 -> 65

**Non-Delaying Stage**

Amplification:  $\beta$  = 1/4,  $C_{L,eff}$  = 1.25pF,  $\beta\omega_{unitv}$  =  $g_m/5pF$

Sampling:  $\beta = 1/2$ ,  $C_{L,eff} = 0.5pF$ ,  $\beta \omega_{unity} = g_m/1pF$

Phase Margin: 73 -> 33

#### NLCOTD: Wide-Swing Cascode Current Mirror

ECE1371 8-49

### **What You Learned Today**

- Choice of V<sub>EFF</sub>

Trade-offs with various paramters

- 2. Amplifier Topology

- 3. Amplifier Step Response

- 4. Gain-Boosting

- 5. Choice of Delaying/Non-Delaying Stages